- HBMの検査って、具体的に何をしているの?

- 「プローブカード」「ウェハテスト」「KGD」──用語が多すぎて整理できない

- なぜHBMの検査がAI半導体の供給を制約するボトルネックになっているの?

- アドバンテストやFormFactorがHBM関連で注目される理由が構造的にわからない

- 投資やキャリアを考える前に、検査工程の全体像を把握したい

- HBM検査の全体フロー──ウェハテスト→KGD選別→積層後テスト→バーンインの4段階

- プローブカードの役割と、なぜHBM向けが特別に難しいのか

- KGD(Known Good Die)がコスト構造にどう効くのかを数字で理解

- 検査がAI半導体の供給ボトルネックになっている構造的な理由

- 検査関連の主要企業と市場規模

- 投資家・学生・技術者それぞれにとっての意味

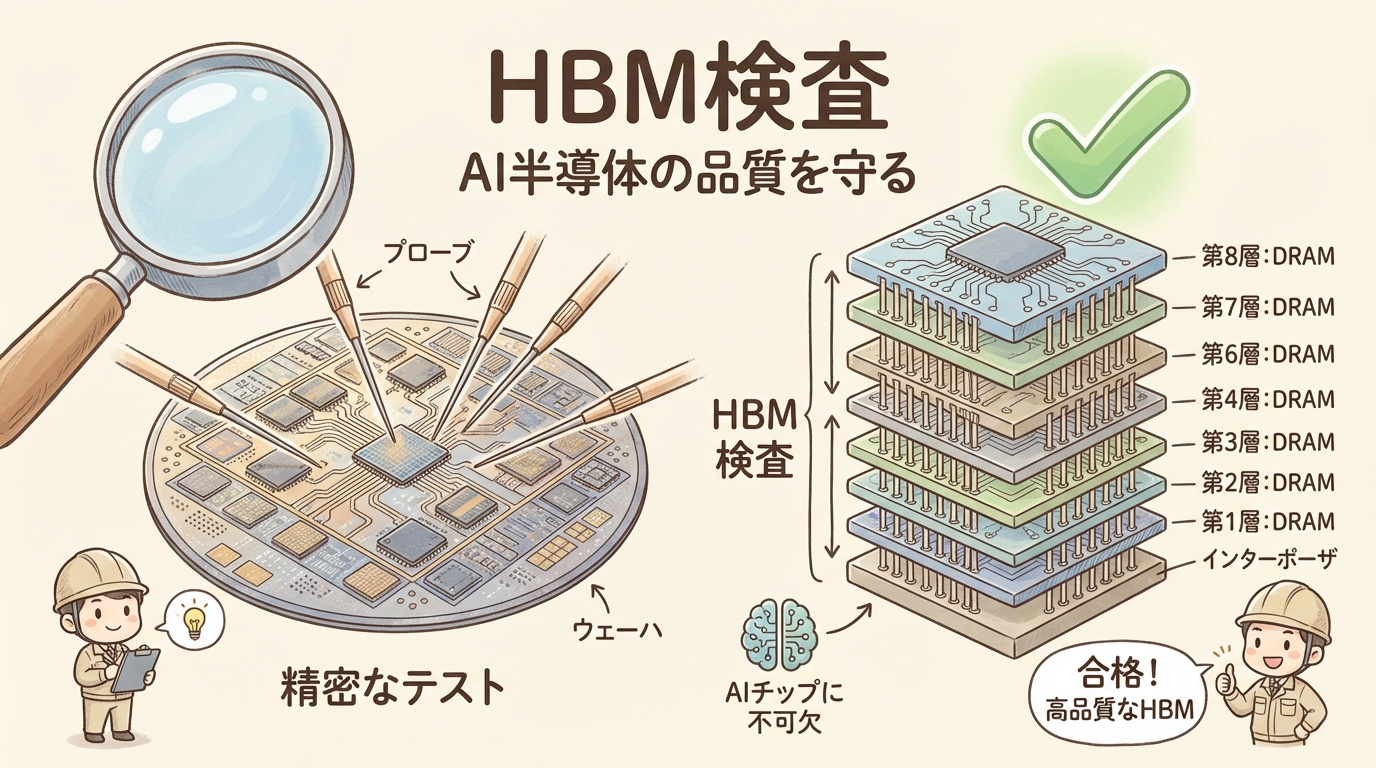

HBM検査とは、複数のDRAMダイを積層する「前」と「後」の両方で、ダイ1枚1枚の電気的特性を超精密に確認する一連のテスト工程です。通常のDRAMテストと決定的に違うのは、「不良ダイを1枚でも積んでしまうと、スタック全体が廃棄になる」という構造的リスクがある点。だからこそ積層前に「Known Good Die(KGD)」──確実に良品と保証されたダイだけを選別する工程が極めて重要になります。さらに積層後も高温バーンインで初期故障品を排除する必要があり、テスト時間はAIチップ全体でCPUの約3倍に達します(出典:Logmi Finance)。検査工程の能力がHBMの供給量を直接左右する──これがAI半導体時代の新しいボトルネック構造です。

「HBMって、積むだけでしょ?」──そう思っていませんか? 実は、HBMの製造で最も神経を使うのは「積む前に、1枚1枚のダイが本当に良品かを確認する」工程です。この検査がなければ、数万円のHBMスタックがまるごとゴミになるリスクがあります。

この記事では、HBM検査の仕組みを4つのステップで図解し、なぜ今「テスト工程」がAI半導体の供給を左右するボトルネックになっているのかを構造的に解説します。

- HBM検査の全体像──まず「4つの検査ステップ」を地図にする

- STEP 1 ウェハテスト──プローブカードで「ダイ1枚ずつ」に触れる

- STEP 2 KGD選別──「良品ダイだけ」を積層に送る門番

- STEP 3 積層後テスト──「スタック全体」が正しくつながっているか

- STEP 4 バーンイン──高温で「初期不良」をあぶり出す

- なぜHBM検査がAI半導体の「ボトルネック」になっているのか

- HBM検査を支える主要企業──テスター・プローブカードの産業地図

- HBM検査の市場規模と成長見通し

- よくある誤解を整理する

- あなたにとっての意味──投資家・学生・技術者の視点

- まとめ──HBM検査の全体像

- ❓ よくある質問(FAQ)

HBM検査の全体像──まず「4つの検査ステップ」を地図にする

🗺️ 製造フローのどこで、何を検査するのか

HBMの検査は、1回やれば終わりではありません。DRAMウェハーの製造から最終出荷まで、少なくとも4段階の検査が繰り返されます。まず全体の地図を俯瞰しましょう。

電気的特性を検査

積層工程に送る

動作・接続を確認

強制的にあぶり出す

HBMの検査は「高層マンションの建設」に似ています。STEP 1で「レンガ1個ずつ」の品質を確認し、STEP 2で「使えるレンガだけ」を選別する。STEP 3で「積み上げたフロア全体」が歪んでいないか確認し、STEP 4で「地震シミュレーション(高温負荷)」をかけて初期に壊れるものを除外する。1個でも不良レンガが混じれば、フロアごと崩壊する──だから「積む前の選別」が命なのです。

通常のDRAMでは「ウェハテスト→最終テスト」の2段階で済むことが多いですが、HBMは「積層」という不可逆な工程が入るため、検査の回数と精度が桁違いに求められます。積層後に不良が見つかっても、積み直しはできない──この構造的な特性が、HBM検査を特別なものにしています。

STEP 1 ウェハテスト──プローブカードで「ダイ1枚ずつ」に触れる

📋 切り出す前に、ウェハー上で全ダイを電気的にテスト

HBM検査の最初のステップはウェハテスト(Wafer Probe Test)です。製造されたDRAMウェハーを切り出す前に、ウェハー上の全ダイ1枚1枚に対して電気的な動作確認を行います。

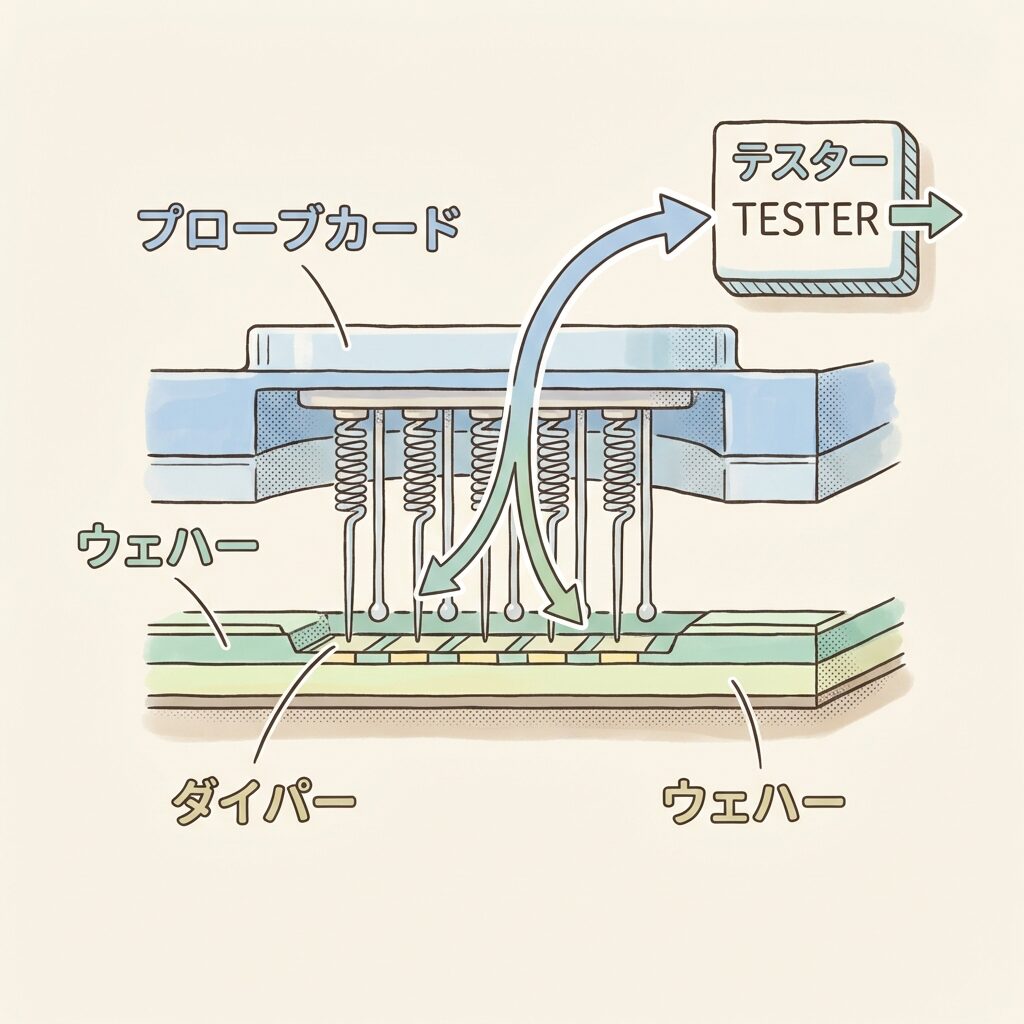

シリコンウェハーからダイを切り出す前に、ウェハー上の各ダイの電極パッドに微細な針(プローブ)を接触させ、電気信号を送受信して動作を確認するテスト工程。不良ダイを早期に発見し、後工程のコストを削減する「水際検査」の役割。

このとき、ウェハー上のダイに電気信号を送るために使う道具がプローブカードです。プローブカードは、数千〜数万本の超微細な針(プローブ)が精密に配置された検査治具で、ウェハー上のダイの電極パッドに物理的に触れて電気を流します。

ウェハーテスト時に、ダイの電極パッドに物理的に接触して電気信号を送受信するための精密治具。数千〜数万本のMEMS(微小電気機械システム)プローブ針が、マイクロメートル単位の精度で配列されている。テスト装置(テスター)とウェハーを「つなぐ橋」の役割(出典:Technoprobe社プレゼンテーション)。

生成・判定

物理的に接触

1枚ずつ確認

ウェハテストで確認する項目は多岐にわたります。メモリセルの読み書き速度、データ保持時間(リフレッシュ特性)、消費電流、各端子の電圧レベル、TSV(貫通電極)の接続状態などです。アドバンテストのIR技術説明会資料によれば、HBMの積層後ウェハテストは基本的に通常のメモリテストと同じテスターで行えますが、テスト条件が大きく異なることが特徴です(出典:アドバンテスト IR技術説明会 Q&A)。

📌 なぜHBM用プローブカードは「特別に難しい」のか

プローブカードはDRAM・ロジックICなどさまざまな半導体のテストに使われますが、HBM向けのプローブカードは通常品と比べて格段に難しい技術要求を突きつけられています。その理由を3つに分けて整理します。

Korea Instrument(KI)社は、HBM向けプローブカードの開発においてテスト装置メーカーとの「共同開発」の重要性を強調しています。HBM世代が進むごとに、より微細なピッチ・より大きな電流・より高い信号品質が求められ、プローブカード単体ではなくテスター全体との最適化が不可欠になっているためです。

上位数社シェア

年平均成長率(〜2026年)

(2024年・推定)

プローブカード市場は寡占構造です。FormFactor(米)とTechnoprobe(伊)が世界の上位シェアを占め、日本では日本マイクロニクス(MJC)と日本電子材料が健闘しています。Intel Market Researchの調査によれば、先端プローブカード市場は2024年に約24億ドル、2032年には約36億ドルに達する見通しです(出典:Intel Market Research)。

STEP 2 KGD選別──「良品ダイだけ」を積層に送る門番

✅ なぜ「Known Good Die」がHBMのコストを左右するのか

ウェハテストで電気的特性を確認した後、基準をクリアしたダイだけがKGD(Known Good Die=良品保証済みダイ)として積層工程に進みます。この「門番」の精度が、HBMの製造コストを根本から左右します。

ウェハテストの結果、電気的に良品と確認されたダイのこと。3D積層やチップレット設計では、不良ダイを積んでしまうとパッケージ全体が無駄になるため、積層前のKGD選別精度が製造コストに直結する。ソニーセミコンダクタの品質ハンドブックでは、KGDの他にKTD(Known Tested Die)、PD(Probed Die)など選別精度のグレードが定義されている(出典:ソニーセミコンダクタ 品質・信頼性ハンドブック)。

なぜKGDがこれほど重要なのか? 数字で考えてみましょう。

8枚積層のHBM3Eスタック。各ダイの良品率95%とすると、スタック全体の良品率は 0.95⁸ ≒ 66%。3個に1個が廃棄──コストが大幅に膨らむ。

ウェハテストで不良ダイを排除し、良品率99.5%以上のダイだけを積層。スタック良品率は 0.995⁸ ≒ 96%。廃棄率が激減し、コスト構造が劇的に改善。

8層スタック良品率

8層スタック良品率

1スタック積層数

東京エレクトロンの技術レポートでも、「KGD選別精度の向上が、3D DRAMの製造コストを直接的に左右する最重要課題のひとつ」と指摘されています(出典:東京エレクトロン 技術レポート 2026年4月)。HBM4ではさらに積層数が12枚以上に増える可能性があり、KGD選別の精度はますます重要になります。

「ウェハテストで良品と判定されたダイ=KGD」ではありません。KGDは単にウェハテストに合格しただけでなく、積層後にも正常に動作することが保証されたダイを指す概念です。そのため、通常のウェハテストよりも厳しい基準が設定されることがあり、テスト項目も多くなります。EDN Japanでは「KGDを使わない場合、大きなコスト増につながる」と警告しています(出典:EDN Japan)。

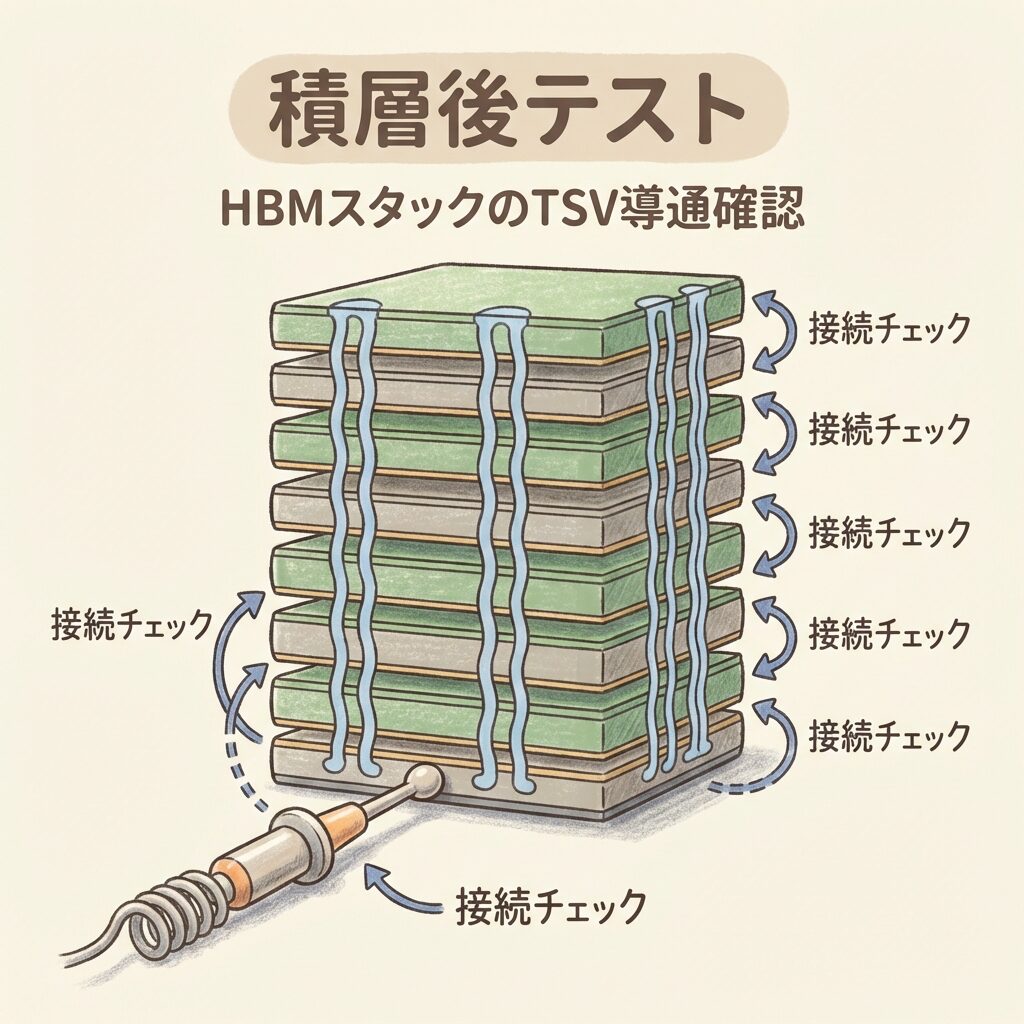

STEP 3 積層後テスト──「スタック全体」が正しくつながっているか

🏗️ 個々のダイは良品でも、積んだら動かない──「接続不良」のリスク

KGD選別で「確実に良品」と判定されたダイを積層しても、安心はできません。TSV(貫通電極)の接合不良、ダイ間の位置ずれ、熱膨張率の差による応力──「積む」という行為自体が新たな不良原因を生むからです。

個々の部品は全部検品済みの「完璧なパーツ」。でも、それを組み立てたら歯車が噛み合わなかった──ということは製造現場ではよくある話です。HBMの積層後テストは、「完成品の動作確認」に相当します。レゴブロックが1個ずつは完璧でも、組み上がった城が傾いていないかは別の検査が必要なのです。

積層後のテストでは、スタック全体としてのメモリ読み書き速度、TSV経由の信号品質、帯域幅性能、消費電力、温度特性などが確認されます。このテストにはTeradyne社のMagnum 7Hテスターのように、HBM3/3E・HBM4/4Eに対応し、最大4.5 Gbps・9,216本のデジタルピンをサポートする高性能テスターが使用されます。

| 検査項目 | 確認内容 | 不良が見つかった場合 |

|---|---|---|

| メモリ機能 | 全セルの読み書き・リフレッシュ | スタック廃棄 |

| TSV接続 | 層間の電気的導通・信号品質 | スタック廃棄 |

| 帯域幅性能 | 規格速度(例:HBM3Eで1.2TB/s/スタック)の達成 | 速度グレード選別 |

| 温度特性 | 高温環境での動作安定性 | 等級分けまたは廃棄 |

Teradyne社は「Known Good Stack Die(KGSD)」という新しい概念を提唱しています。これは個々のダイ(KGD)だけでなく、「積層されたスタック全体が良品であること」を保証する考え方です。また「Chip on Wafer(CoW)」テスト──積層をウェハー上で行い、ウェハー状態のままテストする手法も導入され始めています。

STEP 4 バーンイン──高温で「初期不良」をあぶり出す

🔥 出荷前に「壊れやすいもの」を意図的に壊しておく

積層後テストに合格したスタックにも、もうひとつ関門が待っています。バーンイン(Burn-In)──高温環境下で一定時間動作させ、初期不良品をあぶり出すストレステストです。

半導体デバイスに通常の使用条件よりも厳しい温度・電圧をかけて一定時間動作させ、初期故障( early failure / infant mortality)を強制的に引き起こすスクリーニング手法。「出荷前に弱いものを壊しておく」ことで、市場に出てからの不良率を大幅に下げる(出典:Triotech)。

バーンインは「靴を買ったときの試し履き」に似ています。店で足に合っているように見えても、実際に数時間歩くと靴擦れが起きることがある。半導体も同じで、テストでは合格しても、実際に高温で動かし続けると「生まれつき弱い」ものが壊れる。その「弱いもの」を出荷前にふるい落とすのがバーンインです。

HBMのバーンインは、通常のDRAMのバーンインと比べて2つの点で格段に難しくなっています。

発熱量の巨大化

HBMスタックは8〜12層のDRAMが密集しているため、テスト中の発熱が大きい。アドバンテストの技術資料では「HBMなど積層メモリは高発熱デバイスであり、テスト中の精密な温度制御が不可欠」と記されている(出典:テクノプロデューサー / アドバンテスト知財戦略)。アドバンテストの7038 Single Test Rackは液冷で1サイトあたり最大1.4kWの発熱に対応。

テスト時間の長大化

HBMを含むAIチップのテスト時間は、CPUの約3倍に達するとされている。テスト装置のコストも従来機種の約2倍。テスト時間が生産スループットを直接制約するため、バーンイン工程のキャパシティが出荷量のボトルネックになり得る(出典:Logmi Finance)。

なぜHBM検査がAI半導体の「ボトルネック」になっているのか

⏳ テスト工程が生産スピードの「蛇口」を絞っている

HBMの供給制約というと、「ウェハーの生産量が足りない」「TSVの歩留まりが低い」というイメージを持つ方が多いかもしれません。しかし2025〜2026年の業界動向を見ると、テスト・検査工程そのものがHBM供給のボトルネックになりつつある構造が浮かび上がっています。

テスト時間がCPUの3倍。AIチップ(GPU+HBM)のテスト時間はCPUの約3倍。テスト装置の占有時間が長くなり、同じ数の装置で処理できるチップ数が減る。

テスト装置コストが2倍。先端テスト装置はHBM3E/4の高速信号に対応するため複雑化し、従来装置の約2倍のコスト。設備投資の回収期間も長くなる。

検査回数が多い。通常DRAMは「ウェハテスト→最終テスト」の2段階で済むが、HBMは「ウェハテスト→KGD→積層後テスト→バーンイン→最終テスト」と工程が多い。テスト装置の必要台数が増大する。

プローブカード供給もひっ迫。HBM向けプローブカードは技術要求が高く、供給できるメーカーが限られる。プローブカード不足がウェハテストのスループットを制約するケースも発生。Semicon.TODAYの記事では「テスト部材がHBM量産の供給力を規定し始めた」と報じられている(出典:Semicon.TODAY 2026年2月)。

Semicon.TODAYは別の記事で「HBMの供給制約は前工程(ウェハー生産)だけでは解けない。先端実装・テスト工程を含めた全工程のスループット管理が必要」と指摘しています(出典:Semicon.TODAY 2026年3月)。HBMは「メモリ工場の出荷品」ではなく、「品質がプロセス全体に組み込まれた複合完成品」として捉えるべきだ、という視点です。

(対CPU比)

(対従来比)

(2023〜2027年)

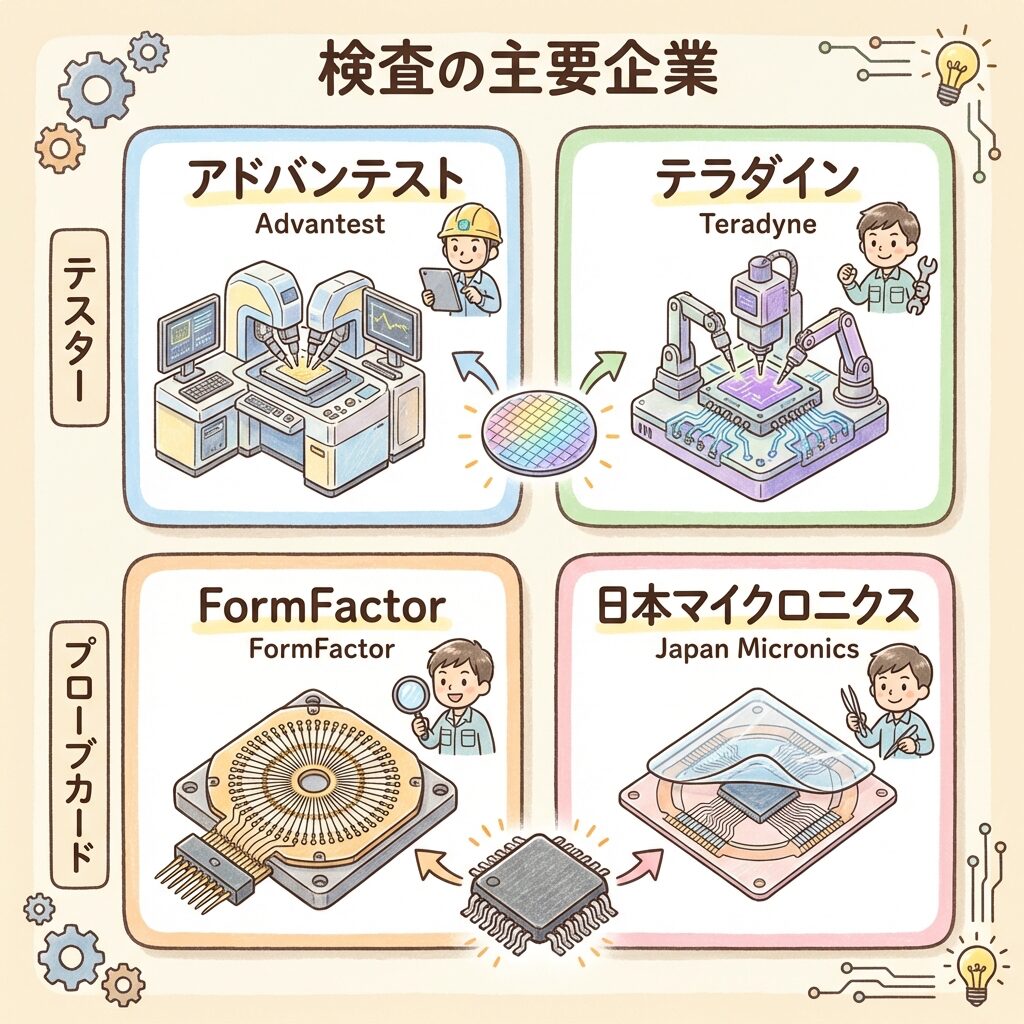

HBM検査を支える主要企業──テスター・プローブカードの産業地図

🏭 「テストの世界」にも寡占構造がある

HBM検査を成立させるには、「テスター(検査装置本体)」と「プローブカード(接触治具)」の2つが揃う必要があります。どちらの市場も、少数の企業が大きなシェアを握る寡占構造です。

| カテゴリ | 企業 | 拠点 | HBM関連の強み |

|---|---|---|---|

| テスター | アドバンテスト | 日本 | T5835メモリテスター。液冷対応7038ラック(1.4kW/サイト)。SLT対応。 |

| テラダイン | 米国 | Magnum 7H。HBM3E/4対応(4.5Gbps・9,216ピン)。KGSD・CoWテスト提唱。 | |

| プローブ カード |

FormFactor | 米国 | HBM向けプローブカードの最大手。FY2026売上予測$930M。HBM4対応で単価上昇。 |

| Technoprobe | イタリア | MEMSベースの精密プローブカード。設計〜製造の垂直統合。 | |

| 日本マイクロニクス(MJC) | 日本 | HBM向けで競争力維持。青森新工場で増産対応。年平均成長率約20%。 | |

| Korea Instrument(KI) | 韓国 | Samsung向け中心。MEMS自社ライン。テスター共同開発に強み。 |

テスター市場はアドバンテストとテラダインの「2強体制」です。Yahoo Financeの報道では「HBMテストはテスト業界の中で最も急成長しているセグメント」と評されています(出典:Yahoo Finance)。AI半導体テストの需要増が、この2社の業績を構造的に押し上げています。アドバンテストのIR資料によれば、HBM市場は2023〜2027年で年平均成長率約52%と、DRAM全体の約21%の2倍以上の成長が見込まれています(出典:アドバンテスト IR技術説明会資料)。

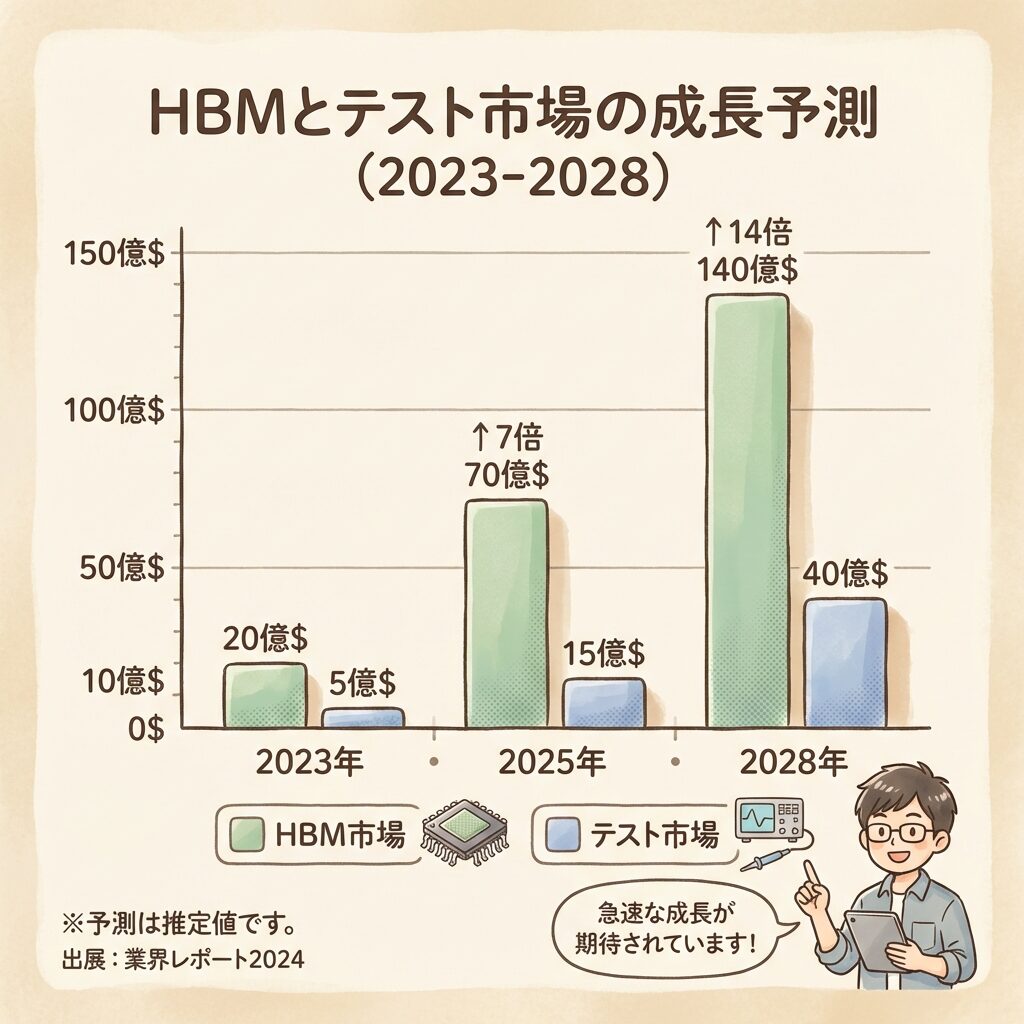

HBM検査の市場規模と成長見通し

📈 HBM市場+52%/年の成長が、テスト市場を構造的に押し上げる

HBM検査の市場を「単独の数字」で切り出すのは難しいですが、関連する市場データを組み合わせることで全体像を把握できます。検査市場の成長は、HBM市場そのものの爆発的成長に連動しています。

(2028年予測・PwC)

(2032年予測)

(2023〜2027年)

PwCのレポートによれば、HBM市場は2028年に約380億ドルに達し、サーバーDRAM市場の約半分、DRAM全体の約28%を占める見通しです(出典:経済産業省 半導体・デジタル産業戦略資料内引用)。この巨大市場の成長は、テスト装置・プローブカード・バーンイン装置の需要を直接的に押し上げます。

さらに、HBMの世代進化も市場を拡大させます。HBM3EからHBM4への移行では積層数が増え、テスト項目が増え、プローブカードの単価も上昇します。FormFactor社は「HBM4向けプローブカードの平均販売価格(ASP)は従来品より大幅に上昇する」と述べています(出典:Seeking Alpha / FormFactor分析)。

よくある誤解を整理する

| ❌ よくある誤解 | ✅ 実際はこう |

|---|---|

| 「HBMの検査は普通のDRAMテストと同じ」 | テスター自体は共通で使えるが、テスト条件・回数・精度が根本的に異なる。積層前のKGD選別、積層後テスト、高温バーンインなど、通常DRAMにはない工程が追加される。 |

| 「テスト工程はコストの小さな部分」 | AIチップのテスト時間はCPUの約3倍、テスト装置コストは約2倍。半導体の製造原価に占めるテスト比率は通常25〜30%とされるが、HBMを含むAIチップではこの比率がさらに上昇している。 |

| 「HBMの供給不足は前工程(ウェハー生産)だけの問題」 | テスト工程・プローブカード供給・バーンインキャパシティなど、後工程全体がボトルネックになり得る。HBMは「ウェハー→積層→テスト→パッケージ」のすべてで能力が揃わないと出荷できない。 |

| 「プローブカードは消耗品だから技術力は低い」 | HBM向けプローブカードはMEMSレベルの精密技術が要求される。微細ピッチ・大電流・高温対応を実現できるメーカーは世界でも限られ、市場は寡占状態。上位数社で約70%のシェアを占める。 |

あなたにとっての意味──投資家・学生・技術者の視点

投資家:HBM検査市場は「AI半導体」の裏側にある構造的な成長領域です。アドバンテスト(6857)、FormFactor(FORM)、日本マイクロニクス(6871)、テラダイン(TER)など、テスト・プローブカード関連企業の売上はHBM出荷量と直接連動します。「NVIDIAの業績が伸びる→HBM需要が増える→テスト需要が増える」というサプライチェーンの因果関係を理解することで、AI投資の視野が広がります。特に、HBM世代が進む(HBM3E→HBM4)ごとにテスト回数・難易度・単価が上がるため、テスト関連企業は量と単価の両方で恩恵を受ける構造です。

学生:半導体テスト工学は「地味」に見えるかもしれませんが、AI時代に最も人材が不足している領域のひとつです。テスト設計、MEMS(プローブカード)、信号解析、熱管理──これらのスキルは電気・電子・機械・材料のすべての学生にとってキャリアの差別化要素になります。「なぜダイを積む前に検査が必要なのか」をKGDの歩留まり計算で説明できるだけで、就活面接での印象は大きく変わるはずです。

技術者:AIシステムの設計・調達を行う技術者は、「HBMの供給制約がどの工程で発生しているか」を知ることで、調達計画の精度が上がります。テスト工程がボトルネックであるなら、テスト装置メーカーの増産計画やリードタイムがHBMの納期に影響します。また、自社製品のテスト設計にKGD・KGSD的な発想を取り入れることで、歩留まり改善のヒントが得られるかもしれません。

まとめ──HBM検査の全体像

① HBM検査は4段階:ウェハテスト(ダイ1枚ずつの電気テスト)→ KGD選別(良品ダイだけを積層へ)→ 積層後テスト(スタック全体の動作確認)→ バーンイン(高温負荷で初期不良を排除)。

② プローブカードが検査の「物理的な接点」:微細な針でダイに触れ、電気信号を送受信する精密治具。HBM向けは微細ピッチ・大電流・高温対応が求められ、供給メーカーは寡占状態。

③ KGDが製造コストを左右する:不良ダイを1枚でも積むとスタック全体が廃棄。KGD選別精度が8層スタックの良品率を66%から96%に引き上げ得る。

④ テスト工程が供給のボトルネック:AIチップのテスト時間はCPUの3倍、装置コストは2倍。プローブカード供給もひっ迫し、テスト能力がHBM出荷量を直接制約する時代に。

⑤ 検査市場はHBM成長と連動:HBM市場は年率52%で成長中。世代進化(HBM3E→4)でテスト回数と単価が上がり、テスト関連企業は量と単価の両方で恩恵を受ける構造。

結局こういうことです。HBMの検査は「品質確認」にとどまりません。検査がHBMの製造コスト・供給量・出荷スピードのすべてを左右する構造的なカギになっています。HBMを「積み重ねたメモリ」としてだけ見るのではなく、「全工程で品質が作り込まれた複合完成品」として捉えることが、AI半導体の産業構造を理解する第一歩です。

❓ よくある質問(FAQ)

📖 【完全図解】先端パッケージとは? AI半導体の「実装革命」を構造で理解する →

この記事は上記ロードマップの一部です。HBM・CoWoS・チップレット・検査──すべてが「先端パッケージ」という幹から枝分かれしたテーマです。全体像から学びたい方はこちらからどうぞ。

📚 次に読むべき記事

HBMの基本を学んでいない方は、まずこの記事から。TSV・3D積層・帯域幅の仕組みを30秒で理解できます。

HBMをGPUと統合するCoWoS技術。テスト済みのHBMがどのようにパッケージされるかを理解できます。

チップレット設計とKGDの関係。分割したダイの品質保証がなぜ重要かが、さらに深く理解できます。

コメント