「先端パッケージ」──AI半導体のニュースで急に見かけるようになったこの言葉、こんなふうに感じていませんか?

- 「先端パッケージ」と「従来のパッケージ」って何が違うの?

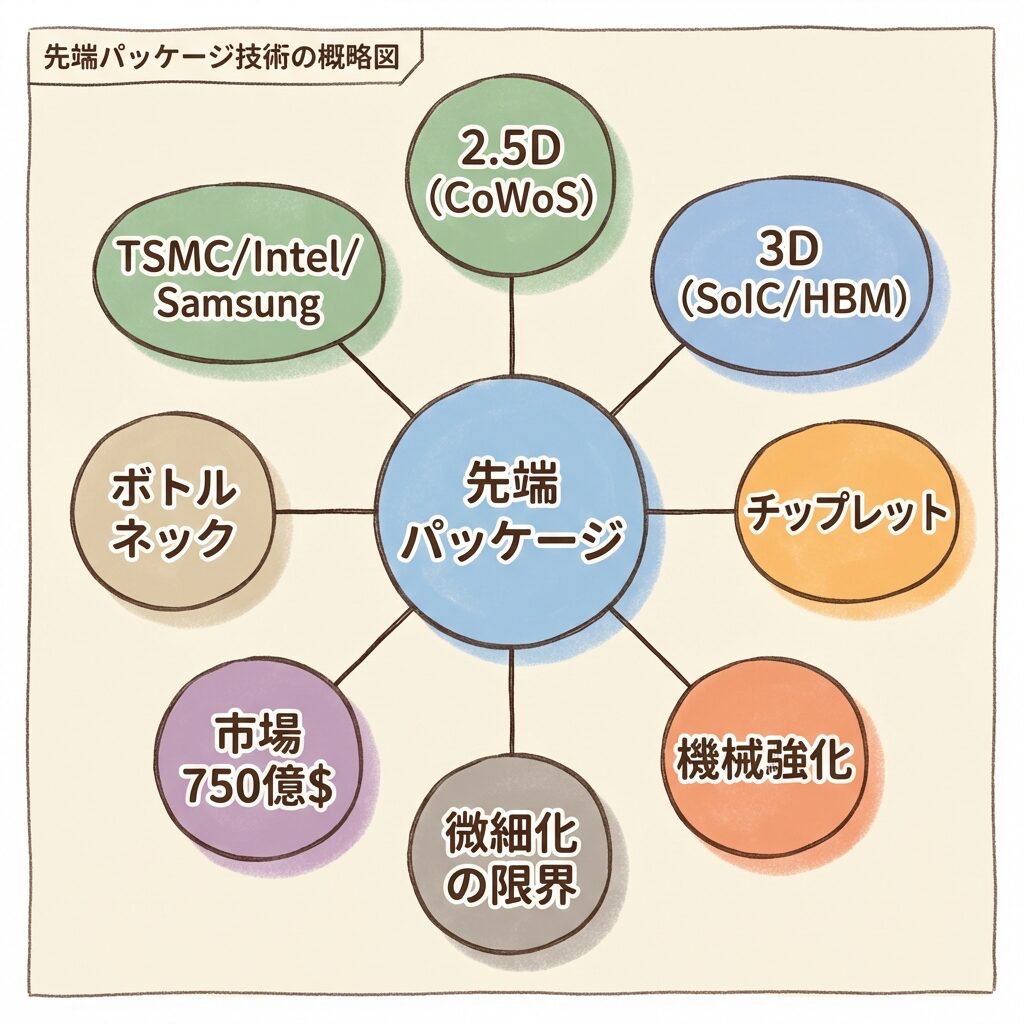

- 2.5D実装、3D実装、チップレット──似た言葉が多すぎて混乱する

- なぜ「チップの微細化」だけじゃなく「組み立て方」が注目されるようになったの?

- CoWoSやInFO、SoICは聞いたことあるけど、全体のなかでどこに位置するの?

- 投資やキャリアを考える前に、まず全体の地図が欲しい

- 先端パッケージの定義と「従来型との決定的な違い」

- なぜ今「チップの微細化」だけでは限界なのか──ムーアの法則の減速

- 2D → 2.5D → 3Dの進化の階段を図解

- チップレットという設計思想とパッケージ技術の関係

- TSMC・Intel・Samsungの主要技術の全体マップ

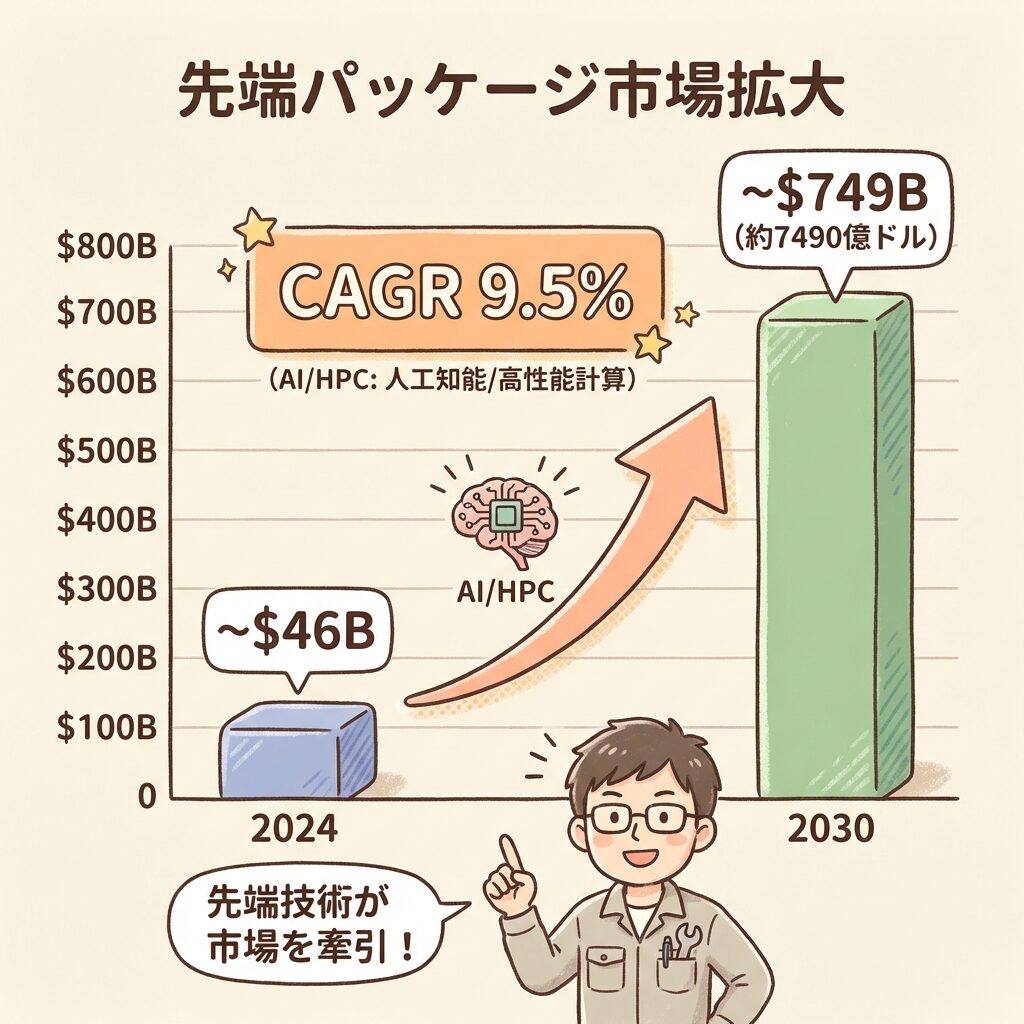

- 先端パッケージ市場が2030年に約800億ドル規模に成長する構造

- 投資家・学生にとっての意味と行動指針

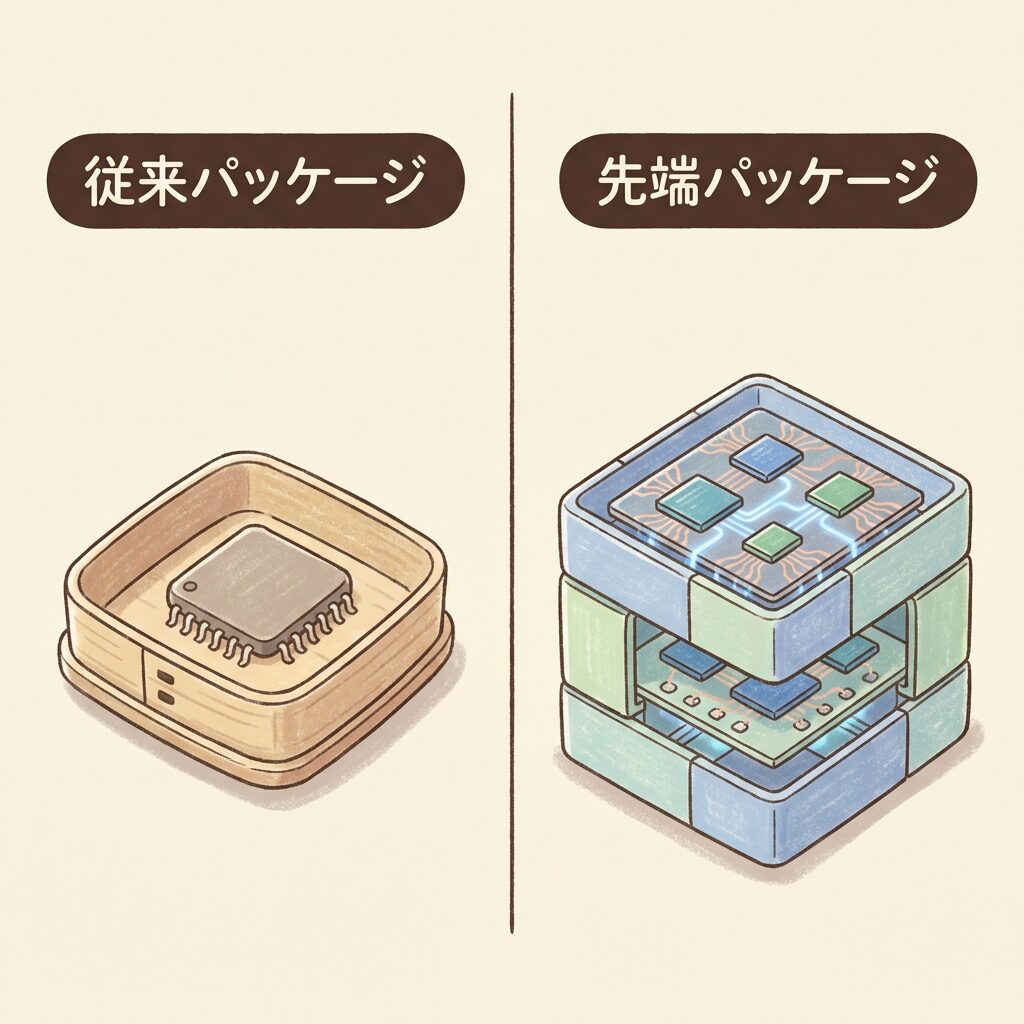

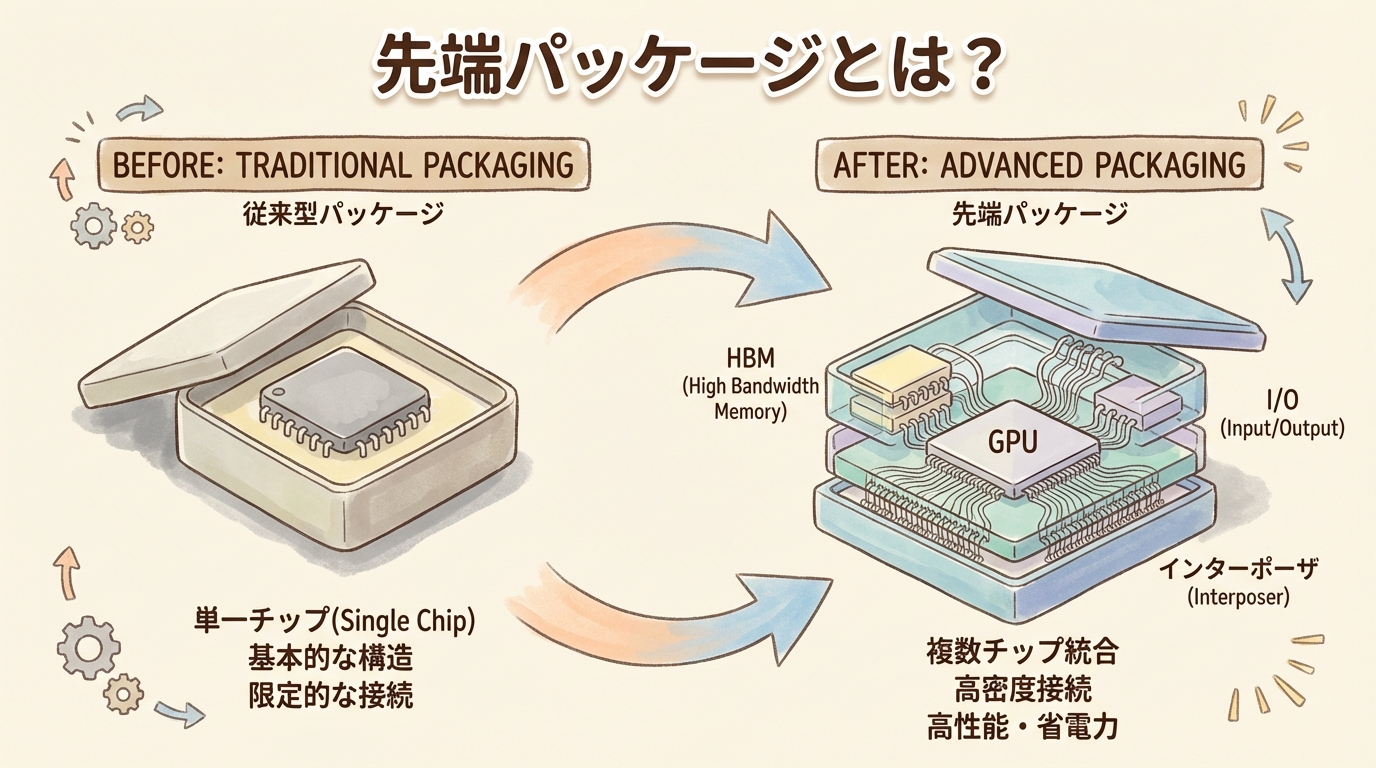

先端パッケージとは、複数の半導体チップ(ダイ)を高密度に統合し、1つの高性能パッケージとして機能させるための実装技術の総称です。従来のパッケージが「1つのチップを1つの箱に入れる」だけだったのに対し、先端パッケージは「GPUとメモリと入出力チップを、超微細な配線で横並びに(2.5D)あるいは縦に積み重ねて(3D)統合する」ことを可能にします。この技術がなければ、NVIDIA H100やB200のようなAI GPUはそもそも製品として成立しません。トランジスタの微細化(ムーアの法則)が物理的・経済的に限界に近づくなか、「チップの作り方」ではなく「チップの組み合わせ方」──すなわちパッケージング技術が、半導体性能向上の新たな主軸になっています。先端パッケージの市場規模はYoleの予測で2030年に約749億ドルに達する見通しです(出典:マイナビニュース / Yole)。

この記事は、当サイトの先端パッケージ関連記事の「全体地図」にあたるピラー記事です。CoWoS、HBM、チップレットといった個別テーマに入る前に、「先端パッケージとは何か」「なぜ今重要なのか」を構造から理解しましょう。

先端パッケージとは?──まず定義を30秒で理解する

📦 「チップの包み方」が進化した技術の総称

半導体パッケージとは、シリコンウェハー上に作られた回路(ダイ)を保護し、外部の基板やマザーボードと接続するための「入れ物」です。いわば半導体チップの「外装」にあたる部分です。

従来のパッケージは「1つのチップを1つの箱に入れる」だけでした。しかし先端パッケージは違います。複数のチップを、超微細な配線で高密度に統合し、1つのパッケージとして機能させる──これが「先端パッケージ(Advanced Packaging)」です。

従来のパッケージが「1人用のお弁当箱」だとすると、先端パッケージは「仕切り付きの多段重箱」です。ごはん(GPU)、おかず(HBM)、漬物(I/Oチップ)をそれぞれ最適な容器で作って、1つの重箱にぴったり詰め合わせる。中の仕切り(インターポーザー)が超精密に設計されているから、箱を開けるだけで全部が連携して動く──これが先端パッケージの発想です。

・1つのチップを1つのパッケージに封入

・ワイヤボンディングやフリップチップで基板に接続

・チップ同士はマザーボード上の配線で通信(遠い・遅い)

・性能向上はチップ内部の微細化に依存

・複数チップを1パッケージに統合

・インターポーザーやTSVで超近距離・超高密度に接続

・GPU+HBM+I/Oが数mm以内で通信(近い・速い)

・チップの「組み合わせ方」で性能向上

シリコンウェハー上に作られた回路(ダイ)を、外部と接続可能な状態にするための工程・技術。チップを保護し、電気的・物理的に基板と接続する「入れ物を作る」工程であり、半導体製造の最終段階(後工程)に位置する。

なぜ今「パッケージ」が主役になったのか──ムーアの法則の減速

📉 「チップを小さくする」だけでは限界が来た

半導体産業はこの50年間、「トランジスタを小さくする(微細化)」ことで性能を上げてきました。これが有名な「ムーアの法則」──約2年ごとにトランジスタ密度が2倍になるという経験則です。

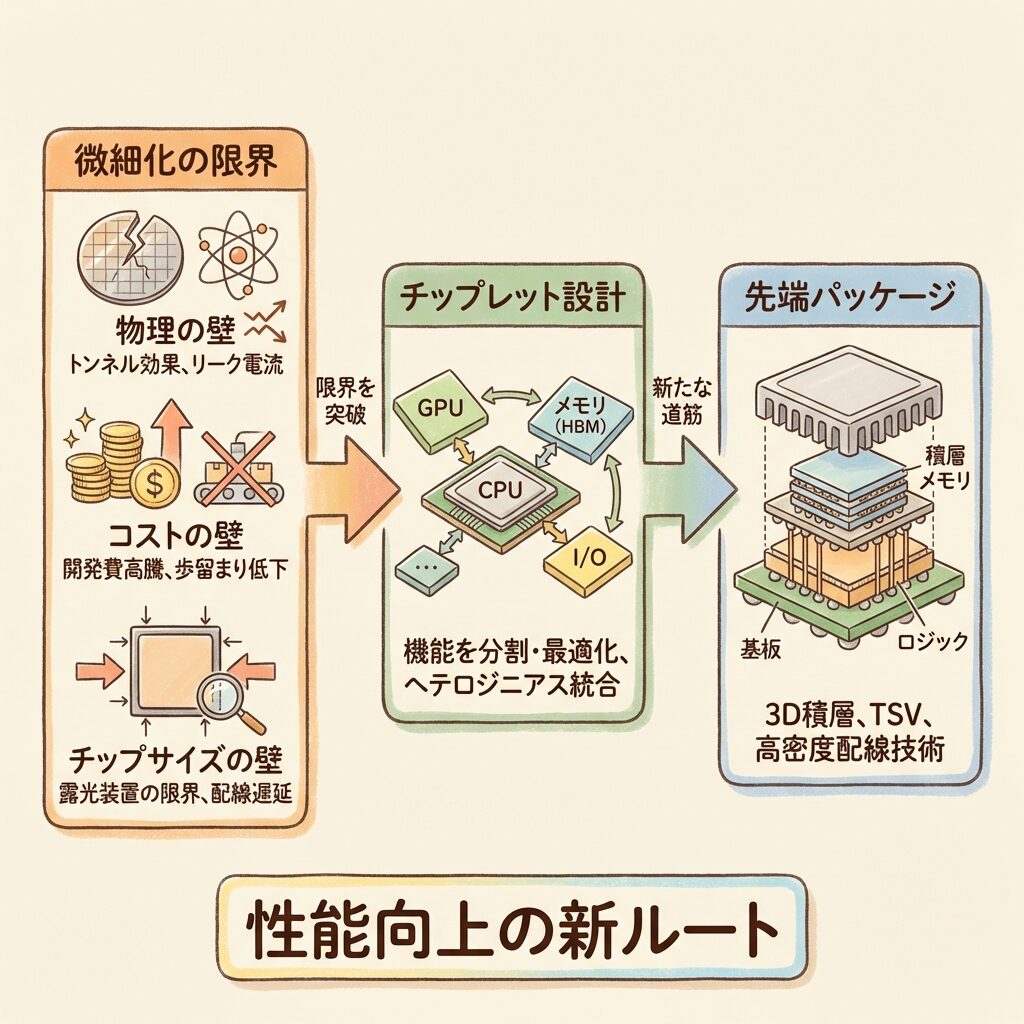

しかし2020年代に入り、この法則に3つの壁が立ちはだかっています。

🔀 「小さくする」から「組み合わせる」へ──パラダイムシフト

これらの限界を突破するために登場したのが、「1つの巨大チップを作る」のではなく「小さなチップを複数作って、高度なパッケージ技術で組み合わせる」というアプローチです。

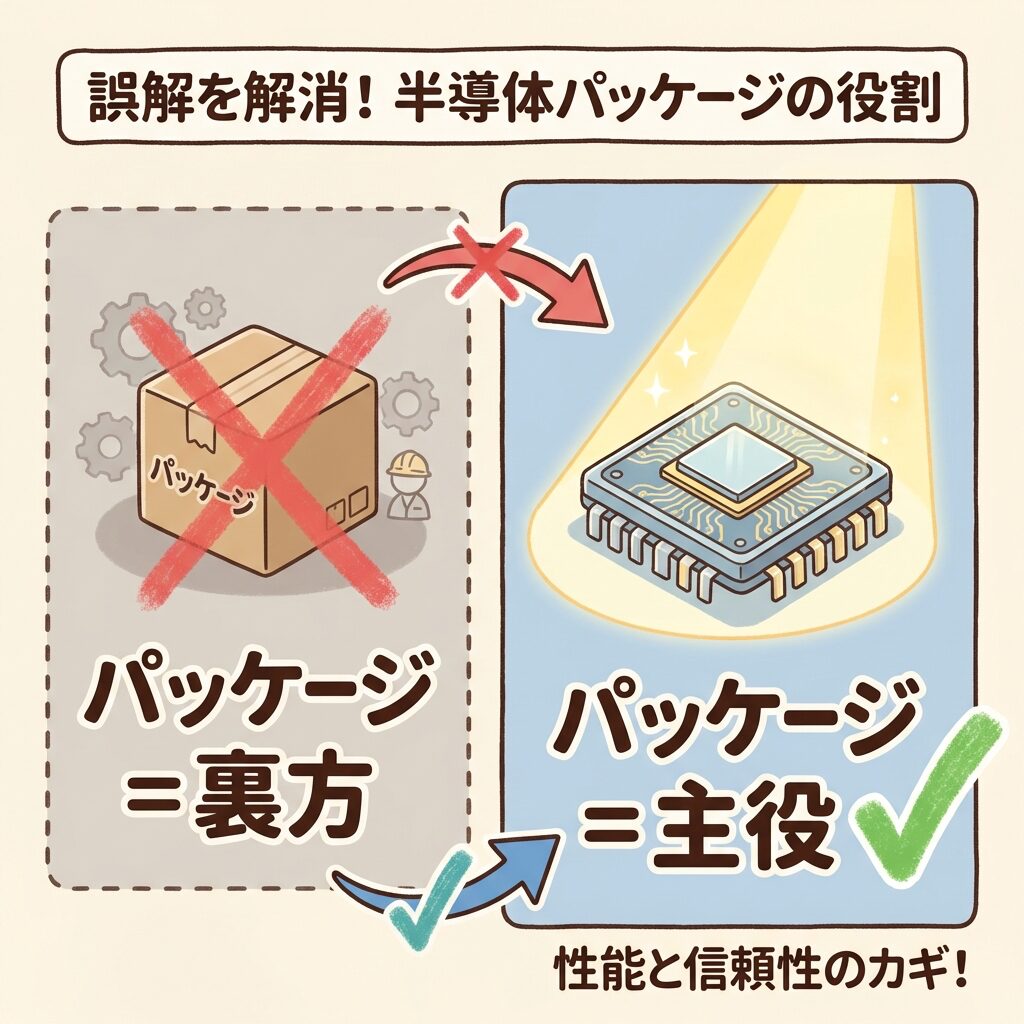

半導体の進化の主軸は、「トランジスタを小さくする(微細化)」から「チップをどう組み合わせるか(先端パッケージ)」にシフトしつつあります。もちろん微細化が終わったわけではありませんが、微細化だけでは性能向上が追いつかなくなった──だからパッケージ技術が「裏方」から「主役」に昇格したのです。SPIEの2026年シンポジウムでも「ムーアの法則の減速に対する解としてのチップレット革命」が主要テーマとして取り上げられています(出典:SPIE)。

Intel共同創業者ゴードン・ムーアが1965年に提唱した経験則。「半導体チップ上のトランジスタ数は約2年ごとに2倍になる」。これにより半導体は世代ごとに高性能・低コスト化してきたが、トランジスタが原子レベルに近づいた近年、この法則の維持が困難になりつつある。

2D → 2.5D → 3Dの「進化の階段」──先端パッケージの3段階

🪜 チップの「並べ方・積み方」で3段階に分かれる

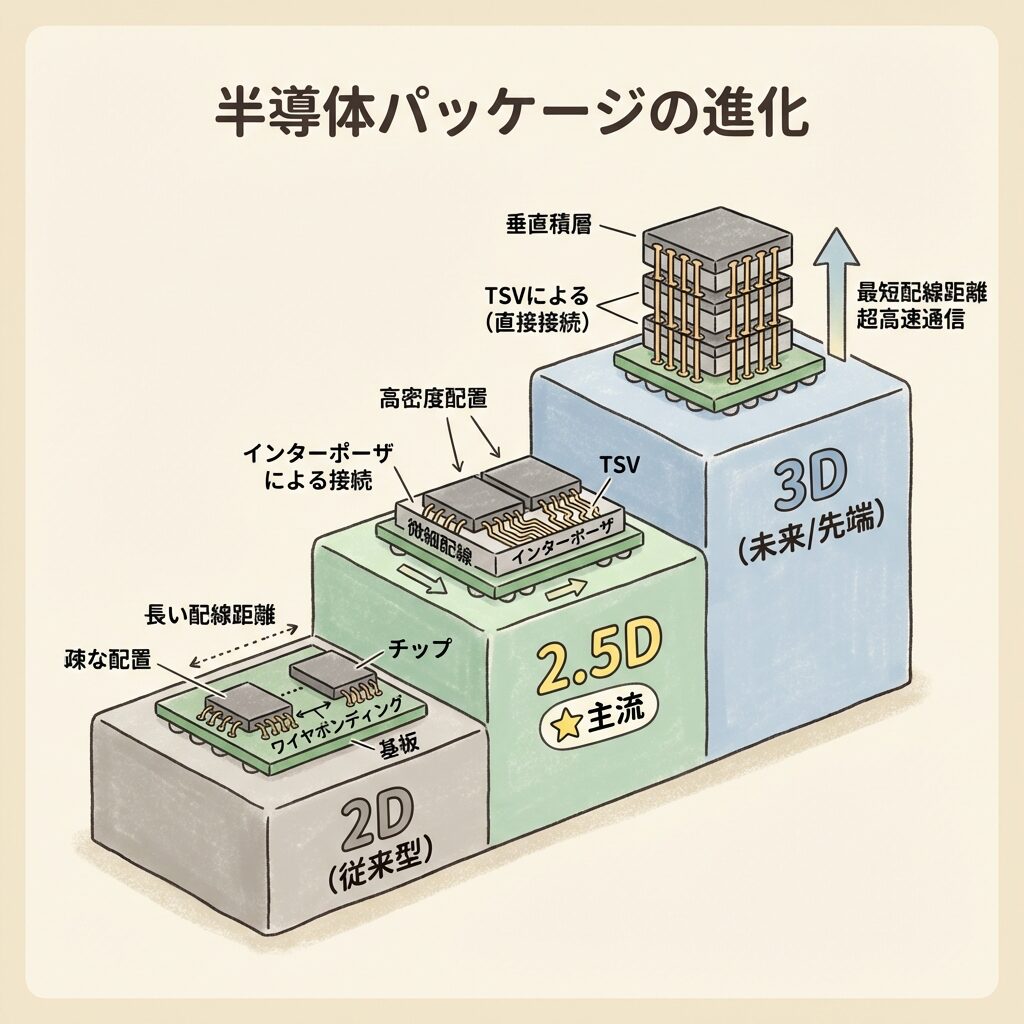

先端パッケージは、チップの統合の仕方によって2D、2.5D、3Dの3段階に分類されます。数字が大きくなるほど統合密度が高く、性能も向上しますが、製造難度とコストも上がります。

チップを基板上に平面的に配置する方式。ワイヤボンディングやフリップチップで基板と接続します。1つのパッケージに1つのチップが基本。複数チップが必要な場合はマザーボード上の配線でつなぎますが、チップ間の距離が遠く帯域幅に限界があります。

複数のチップをインターポーザー(中間基板)の上に横並びに配置する方式。チップ間をインターポーザー上の超微細配線でつなぎ、マザーボード上より圧倒的に近い距離で通信します。GPUとHBMの統合に最適で、現在のAI GPUの主流です。

チップを垂直に積み重ねる方式。TSV(貫通シリコンビア)やハイブリッドボンディングでダイ同士を直接接合します。面積を増やさずに集積度を上げられますが、発熱管理が難しく、製造の歩留まりにも課題があります。

| 比較項目 | 2D実装(従来型) | 2.5D実装 | 3D実装 |

|---|---|---|---|

| チップの並べ方 | 基板上に平面配置 | インターポーザー上に横並び | チップを垂直に積層 |

| チップ間距離 | 数cm(マザーボード上) | 数mm(インターポーザー上) | 数μm(直接接合) |

| 帯域幅 | 低い | 高い | 最も高い |

| コスト | 低い | 中〜高い | 高い |

| 熱管理の難易度 | 容易 | 中程度 | 困難(発熱が集中) |

| 現在の主な用途 | 一般的な半導体 | AI GPU(H100/B200) | HBM・一部ロジック |

「3Dのほうが必ず優れている」と思われがちですが、実際には2.5Dが現在のAI GPUの主流です。3Dは帯域幅では最も有利ですが、発熱の集中と歩留まりの課題が大きく、現時点ではHBM(メモリの積層)や一部のロジックチップに限定的に使われています。2.5Dと3Dを組み合わせるのが、現在の最先端アプローチです。

チップレットとは?──「1枚の巨大チップ」をやめた理由

🧩 機能ごとに分割して、パッケージで再統合する

先端パッケージと切り離せないのが「チップレット(chiplet)」という設計思想です。チップレットとは、1つの大きなチップを機能ごとに小さなダイ(チップ片)に分割し、先端パッケージ技術で再統合するアプローチです。

特定の機能(演算、メモリ、I/Oなど)を担う小さな半導体ダイのこと。それぞれを個別に最適なプロセスで製造し、CoWoSなどの先端パッケージ技術で1つのパッケージに統合する。「レゴブロック」のように組み合わせることから、ヘテロジニアス集積(異種チップ統合)とも呼ばれる。

モノリシック設計(従来)は「1つの巨大な食器に全料理を盛り付ける」方式。皿が大きいほど割れやすく(歩留まり低下)、高くなる。チップレット設計は「小皿料理を個別に作って、重箱に詰め合わせる」方式。小皿は割れにくく(歩留まりが高い)、料理ごとに最適な器を選べる(異なるプロセスの混載)。

・1枚の巨大ダイにすべての機能を集積

・ダイが大きいほど歩留まりが低下(コスト増)

・すべての機能を同じプロセスで製造(最適化が難しい)

・レチクルサイズ(約800mm²)が上限

・機能ごとに小さなダイに分割して製造

・小さいダイは歩留まりが高い(コスト削減)

・機能ごとに最適なプロセスを選択可能(GPU→3nm、I/O→7nm等)

・先端パッケージで統合しレチクル制限を超えられる

NVIDIA Blackwell B200は、このチップレット設計の最先端を体現しています。2つのGPUダイ+8つのHBMスタックをCoWoS-Lで1パッケージに統合──もし1枚のダイですべてを作ろうとしたら、レチクルサイズを大幅に超え、製造不可能です。

チップレットは設計思想であり、先端パッケージは実装技術です。チップレットという「分割の発想」があっても、それを高密度に再統合する「先端パッケージ」がなければ製品にならない。逆に、先端パッケージという「統合技術」があっても、分割されたチップレットがなければ活かす対象がない。両者はセットで意味を持つのです。

先端パッケージの「全体マップ」──主要技術の分類と位置づけ

🗺️ TSMC・Intel・Samsungの技術を一望する

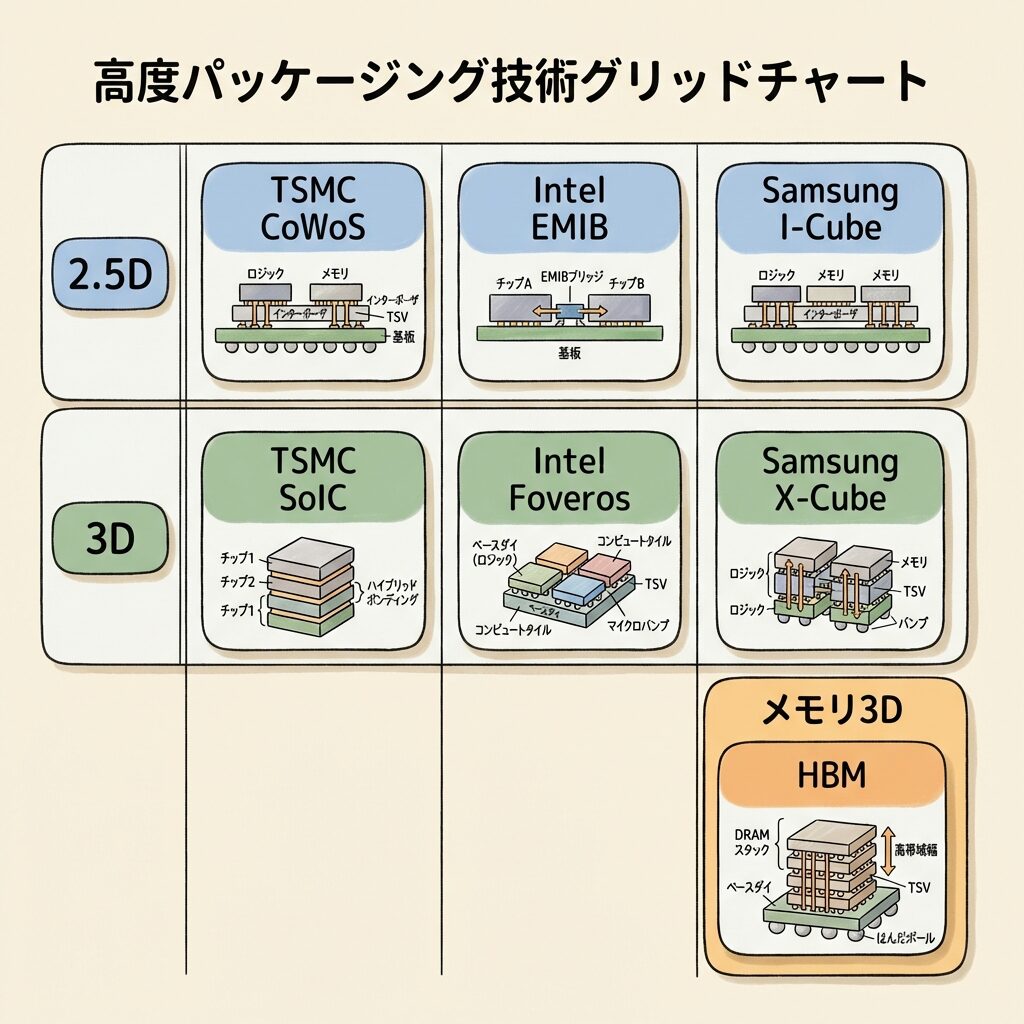

先端パッケージの世界には、各メーカーが独自の名前で開発した技術が多数存在します。名前が似ていて混乱しがちですが、「2.5D」か「3D」かの軸で整理すると全体像が見えてきます。

InFO

(Embedded Multi-die Interconnect Bridge)

(2.5Dシリコンインターポーザー)

(System on Integrated Chips)

(3D ダイスタッキング)

(3D TSV統合)

DRAMダイを3D積層+TSV接続

TSMCはこれらの技術を「3DFabric」というブランドで統合的に提供(出典:TSMC公式)

実際の最先端製品は、2.5Dと3Dを組み合わせて使います。たとえばNVIDIA H100は、HBMスタック(3D積層メモリ)をCoWoS(2.5Dインターポーザー)の上に搭載しています。つまり「3Dで積んだHBMを、2.5Dで横に並べてGPUとつなぐ」──2.5D+3Dの合わせ技が現在の最高性能パッケージです。

HBMとは?GPUの隣にある「AI最重要メモリ」 →

先端パッケージ市場:2030年に約750〜800億ドル規模へ

📈 AI需要がけん引する「年率9〜10%」の高成長

先端パッケージ市場は、AIとHPC(高性能コンピューティング)需要を背景に急成長しています。仏Yole Intelligenceの予測によると、先端パッケージ市場は2024年〜2030年のCAGR(年平均成長率)9.5%で成長し、2030年には約749億ドルを超える見通しです(出典:マイナビニュース / Yole)。セミコンポータルは2032年に約800億ドルと予測しています(出典:セミコンポータル)。

この成長をけん引しているのは、NVIDIA H100/B200に代表されるAI GPU向けのCoWoSパッケージと、HBMのための3D積層実装です。TSMCのCoWoSだけでも、2026年にTSMC売上の約15%を占める見通しです。

先端パッケージは「NVIDIA」や「TSMC」だけの話ではありません。サプライチェーンにはパッケージ基板メーカー(イビデン、新光電気)、実装装置メーカー(ディスコ、東京エレクトロン)、素材メーカー(レゾナック、味の素ファインテクノ)、OSAT(ASE、Amkor)が含まれます。先端パッケージ市場の成長は、これらの「見えにくい企業」に構造的な需要を生みます。

よくある誤解を整理する

| ❌ よくある誤解 | ✅ 実際はこう |

|---|---|

| 「先端パッケージ=チップの微細化」 | 微細化は「チップ内部の回路を小さくする」前工程の技術。先端パッケージは「完成した複数チップを1つにまとめる」後工程の技術。まったく別の工程。 |

| 「3D実装が常に最善」 | 3Dは帯域幅最高だが、発熱と歩留まりの課題が大きい。AI GPUの主流は2.5D(CoWoS)。現実の最先端は2.5D+3Dの組み合わせ。 |

| 「パッケージは裏方の地味な技術」 | AI時代にはCoWoSの生産能力がGPU出荷数を直接制約する最大のボトルネック。「裏方」から「主役」へ完全に昇格。NVIDIAの業績はTSMCのCoWoS能力に依存。 |

| 「先端パッケージはTSMCだけの技術」 | Intel(EMIB/Foveros)、Samsung(I-Cube/X-Cube)も開発・量産している。ただしAI GPU向けではTSMCのCoWoSが圧倒的な実績を持つ。 |

| 「チップレット=先端パッケージ」 | チップレットは「設計思想」、先端パッケージは「実装技術」。両者は表裏一体だが同じものではない。チップレットを実現するための手段が先端パッケージ。 |

あなたにとっての意味──投資家・学生・技術者の視点

先端パッケージ市場は2030年に約750〜800億ドル規模に成長する見通しで、AI GPU需要が構造的にけん引しています。投資テーマとしてNVIDIAやTSMCだけでなく、パッケージ基板(イビデン・新光電気)、実装装置(ディスコ・アドバンテスト)、先端素材(レゾナック・味の素ファインテクノ)、OSAT(ASE・Amkor)まで視野を広げてください。「GPU銘柄」の裏側に、先端パッケージのサプライチェーン全体が広がっています。

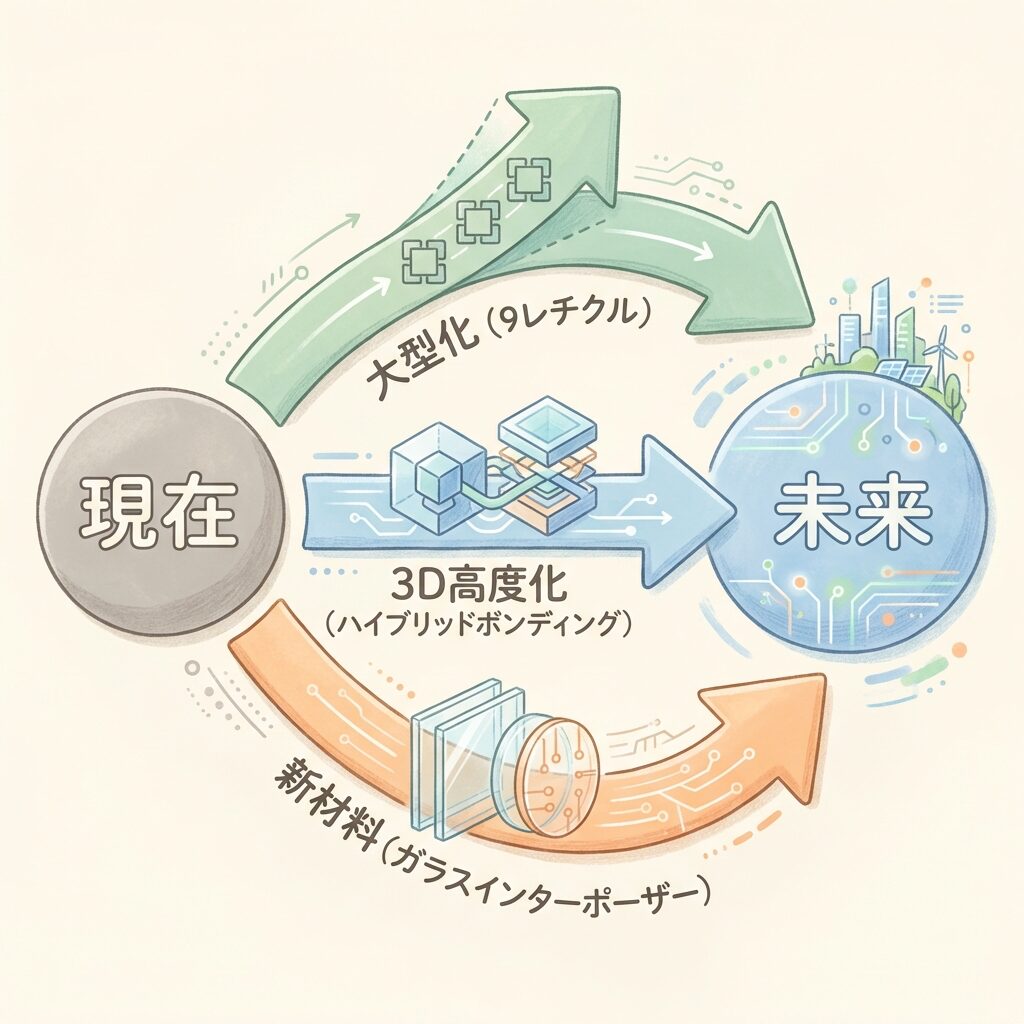

半導体産業の「次の主戦場」はパッケージングです。2.5D/3D実装・TSV・ハイブリッドボンディング・チップレット設計は、今後の半導体エンジニアが必ず直面するテーマ。これは情報系だけでなく、電気工学(信号伝送設計)・材料工学(インターポーザー素材・はんだ材料)・精密機械(実装装置)・熱工学(3D積層の発熱管理)すべてに関わる分野です。「半導体 = 回路設計だけ」という時代は終わりました。

先端パッケージの進化は、データセンターの設計に直接影響します。パッケージの大型化は冷却設計・電力供給・ソケット設計の前提条件を変え、消費電力の増大(B200で1,000W超)は液冷の必須化を加速させています。「チップの中身」だけでなく「チップの包み方」がシステム設計の前提を変えている──これを理解することで、インフラ設計の精度が上がります。

まとめ:先端パッケージの全体像

① 先端パッケージとは:複数の半導体チップ(ダイ)を高密度に統合し、1つの高性能パッケージとして機能させる実装技術の総称。

② なぜ今重要か:ムーアの法則(微細化)の物理的・経済的限界により、性能向上の主軸が「チップの作り方」から「チップの組み合わせ方(パッケージ)」にシフト。

③ 3つの段階:2D(従来型・平面配置)→ 2.5D(インターポーザー上に横並び・AI GPUの主流)→ 3D(垂直積層・HBMなど)。現実の最先端は2.5D+3Dの合わせ技。

④ チップレットとの関係:チップレットは「設計思想」(機能ごとに分割)、先端パッケージは「実装技術」(高密度に再統合)。両者は表裏一体。

⑤ 主要技術:TSMC → CoWoS / InFO / SoIC(3DFabric)、Intel → EMIB / Foveros、Samsung → I-Cube / X-Cube。メモリ → HBM(SK Hynix等)。

⑥ 市場規模:Yole予測で2030年に約749億ドル(CAGR 9.5%)。AI GPU向けCoWoSとHBM需要がけん引。

⑦ ボトルネック:NVIDIAはTSMCのCoWoS-L生産能力の70%超を確保。CoWoSの製造キャパシティがAI半導体供給の蛇口を握っている。

結局こういうことです。半導体の進化は、50年間「チップの中身を小さくする」ことで実現されてきました。しかしAI時代に入り、その限界が明らかになった。そこで「チップの組み合わせ方を変える」ことで性能向上を実現する──これが先端パッケージの本質です。GPUとHBMを超近距離でつなぐCoWoS、DRAMを何層も積み重ねるHBM、機能を小さなダイに分割するチップレット──すべてが「先端パッケージ」という1本の幹から枝分かれした技術です。この全体地図を手に入れたことで、個別テーマの記事がすべてつながるはずです。

❓ よくある質問(FAQ)

📚 次に読むべき記事

先端パッケージの代表格「CoWoS」の仕組み・3種類・ボトルネック構造を解説。この記事の「深掘り版」です。

CoWoSの3バリエーションの違いをインターポーザーの構造から比較。なぜBlackwellがCoWoS-Lを選んだのか。

先端パッケージで統合される「HBM」の仕組み。3D積層・TSV・市場構造を解説。

なぜ「普通のメモリ」ではなくHBMが必要なのか。先端パッケージが前提となる理由がわかります。

先端パッケージで製造されたGPUが大量に並ぶ「AIデータセンター」の全体構造を俯瞰。

📩 記事の更新情報を受け取りたい方へ

新しい記事が公開されたら、Xアカウント @shirasusolo でお知らせします。AIインフラの構造を一緒に学んでいきましょう。

コメント