- 「前工程」「後工程」とよく聞くけど、何がどう違うのか説明できない

- TSMC、ASML、信越化学…名前は知ってるけど、それぞれが半導体製造のどこに位置するのかわからない

- EUVやHBMのニュースを読んでも、全体のどの部分の話かピンとこない

- 半導体株に投資したいが、「装置」「材料」「ファウンドリ」の関係が頭の中で繋がらない

- 半導体製造プロセスの「前工程」と「後工程」の決定的な違い

- 前工程9プロセス・後工程7プロセスの役割と並び順

- 各工程で活躍する装置メーカー・材料メーカー・ユーザー企業

- AI時代に「後工程」の地位が急上昇している構造的理由

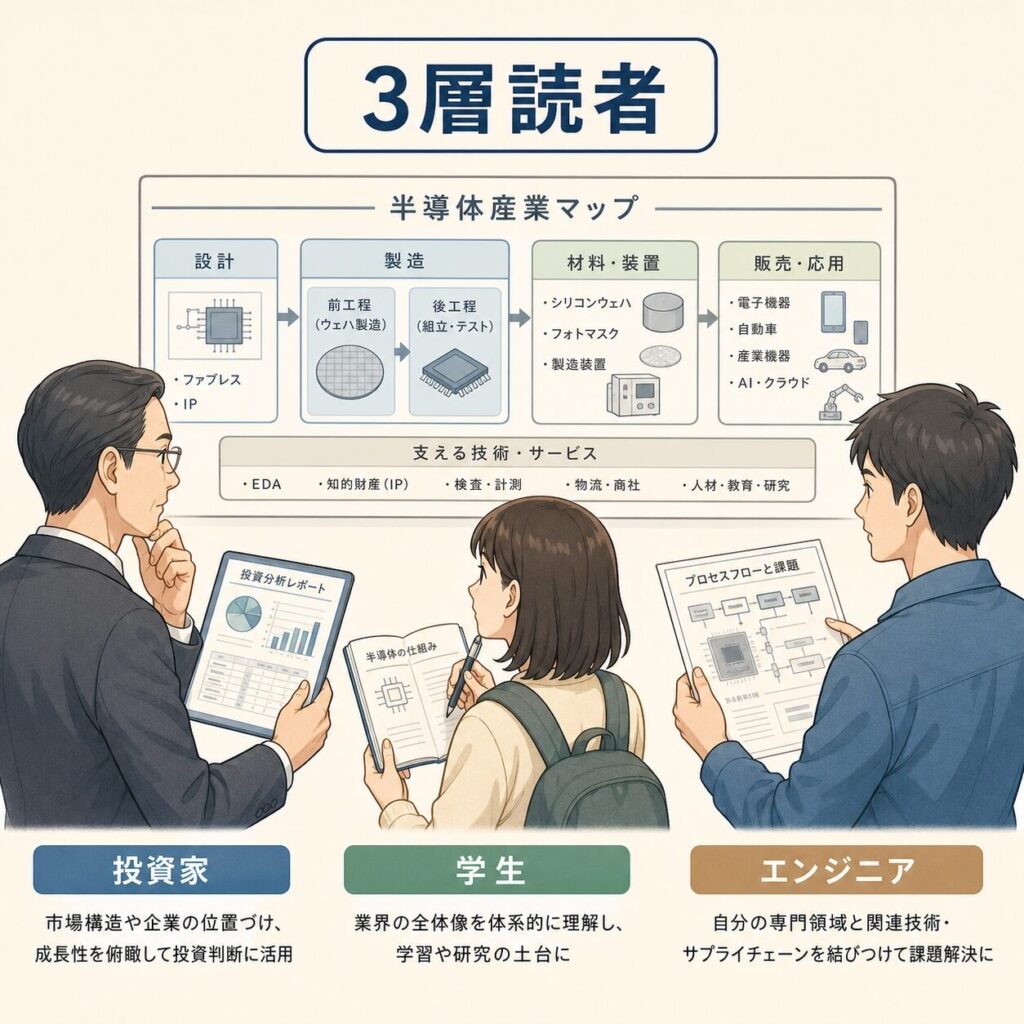

- 投資家・学生・技術者それぞれにとっての意味

半導体のニュースは毎日のように飛び込んできますが、「結局どの工程の話なのか」が掴みにくいですよね。AI半導体、HBM、CoWoSの最先端パッケージ、ASMLのEUV独占、信越化学のシリコンウェーハ……これらは全部「半導体製造」という大きな流れの中の違う場所で起きている話です。

この記事では、半導体製造の全体像を「1枚の地図」として整理します。読み終えるころには、どんな半導体ニュースを見ても「あ、これは前工程の◯◯の話だな」「これは後工程の先端パッケージの動きだな」と即座に位置づけられるようになります。

この記事は、以下のすべてのプロセスをカバーする「全体地図」です。各工程の詳細記事は本記事の最後にリンクしています。

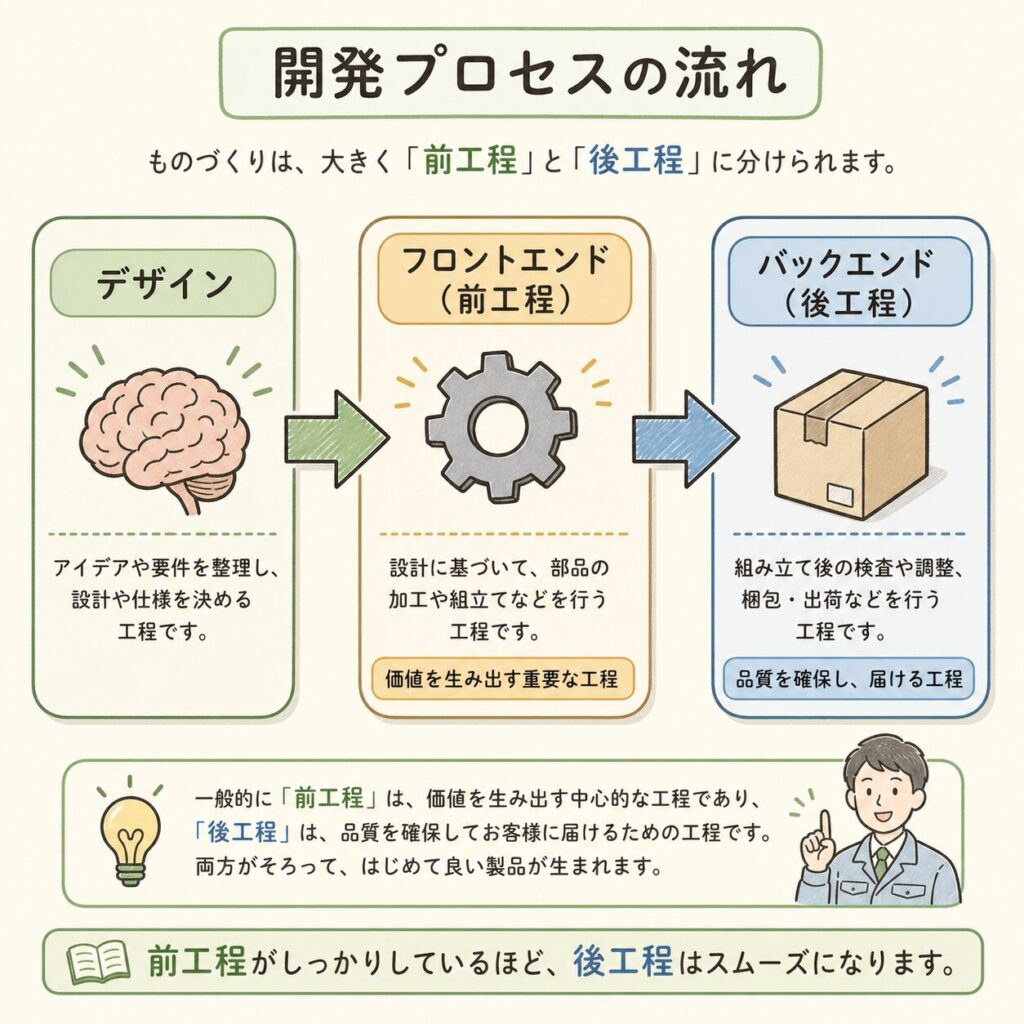

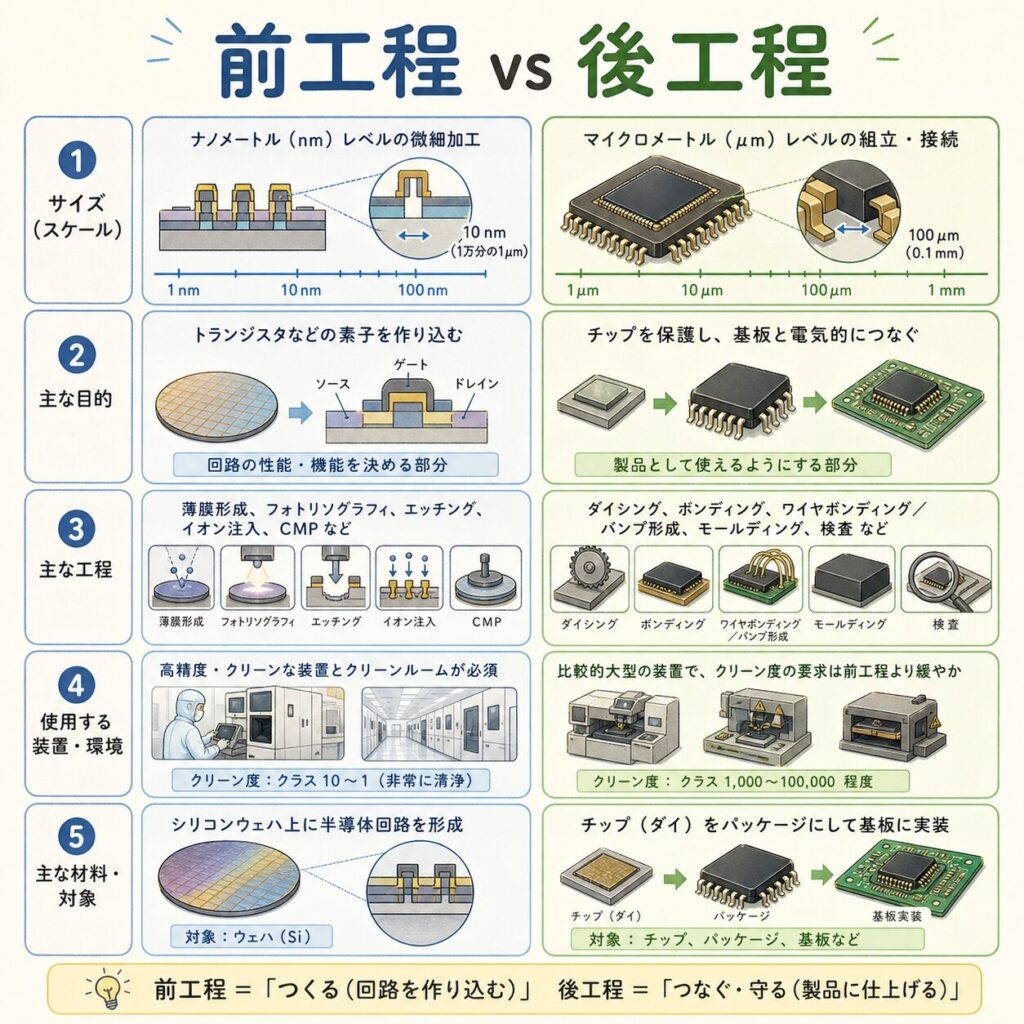

半導体製造は、大きく 「前工程」(ウェーハに回路を作り込む工程) と 「後工程」(ウェーハをチップに切り分けてパッケージ化する工程) の2つに分かれます。前工程はナノメートル精度で9つの主要プロセスを繰り返し、後工程はマイクロメートル精度で7つのプロセスを経て製品化されます。AI時代に入り、後工程の「先端パッケージ」が新たな主役に浮上しています。

まずは全体像を「1枚の地図」で

半導体ができるまでの流れは、大きく分けると 「設計 → 前工程 → 後工程」 の3フェーズです。このうち本記事で扱うのは 「製造プロセス」つまり前工程と後工程。設計(NVIDIA、AMD、Apple等のファブレス企業の領域)はソフトウェアに近い世界なので、別記事でカバーします。

(ファブレス領域)

回路を作る

パッケージ化

※ 本記事のスコープは中央と右の2フェーズ

半導体製造は「お弁当作り」に似ています。設計は「メニューを考える」段階、前工程は「お米を炊いて、おかずを作る」段階、後工程は「弁当箱に詰めて、ラップして、配送する」段階。全部が揃わないと食卓には届きません。

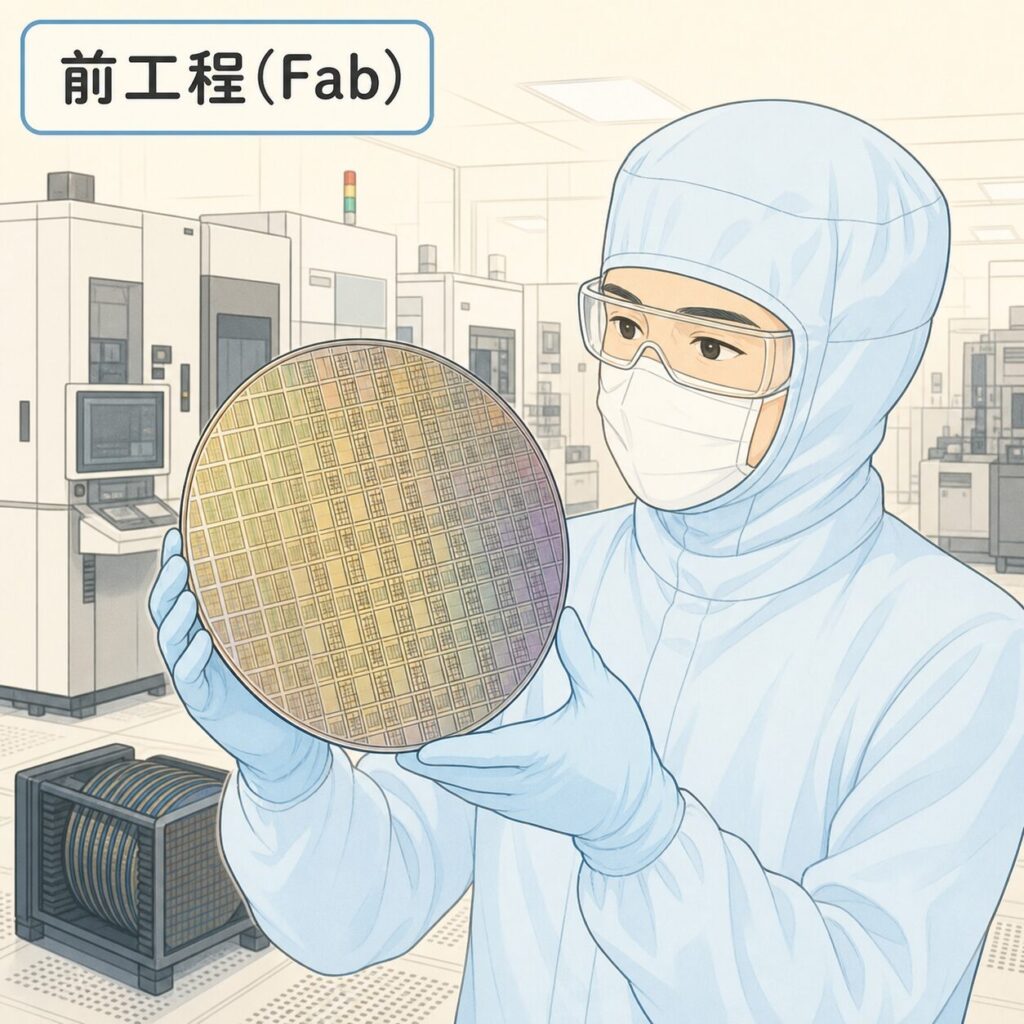

前工程とは?──ウェーハの上に「回路」を作り込む工程

前工程は、英語で Wafer Fabrication(ウェーハファブリケーション)、略して「Fab(ファブ)」と呼ばれます。直径300mmの円盤状のシリコンウェーハの表面に、ナノメートル単位の精度でトランジスタと配線を作り込んでいく工程です。

シリコン(ケイ素)を高純度に精製して作る薄い円盤。直径200mm/300mm/450mmなどがあり、最先端は300mmが主流。1枚のウェーハから数百〜数千個のチップが取れます。

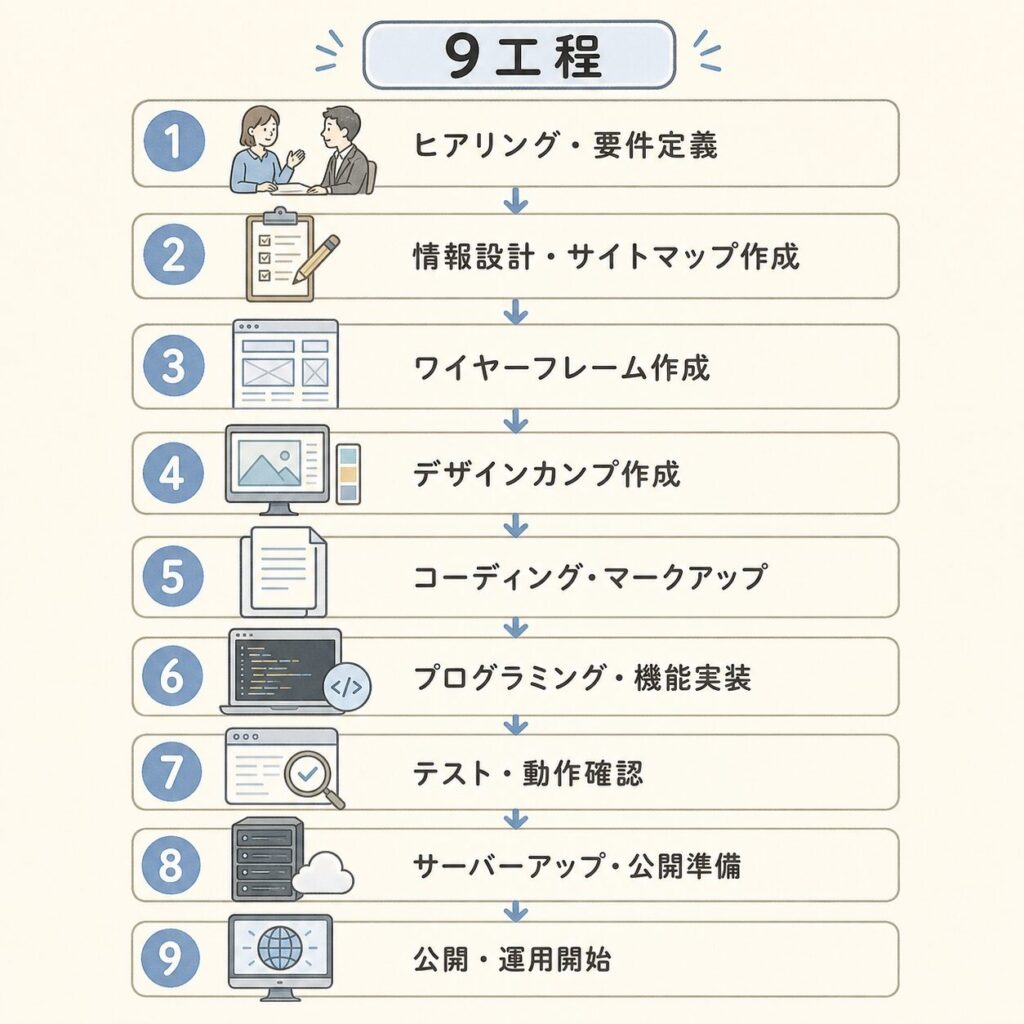

前工程の9つの主要プロセス

前工程は、以下の9つの工程を 「何度も繰り返して」 多層の回路を積み上げていきます。最先端のチップでは、これらの組み合わせを 500〜1,000回以上 繰り返すと言われます。

シリコンウェーハを準備する。SiC・GaNなどの化合物半導体もここに含まれる。

ウェーハ表面に、絶縁膜・金属膜・半導体膜などの「薄い膜」を均一に作る。CVD・PVD・ALDなどの方式がある。

回路パターンを「光で焼き付ける」工程。EUVなど最先端露光技術が使われる、前工程の最重要パート。

露光で「焼き付けたパターン」に従って、不要な部分を「削り取る」工程。

シリコンに不純物を打ち込んで、電気的な特性(N型・P型)を作る。トランジスタの本質。

層を積むたびに表面を「鏡面に磨く」。次の層を綺麗に積むための平坦化工程。

工程の合間に何十回も行われる、ナノレベルの汚れを取る工程。

トランジスタ同士を銅配線でつなぐ。前工程の後半部分にあたる。

各工程の合間に、線幅・欠陥・ズレをナノ単位で計測する。

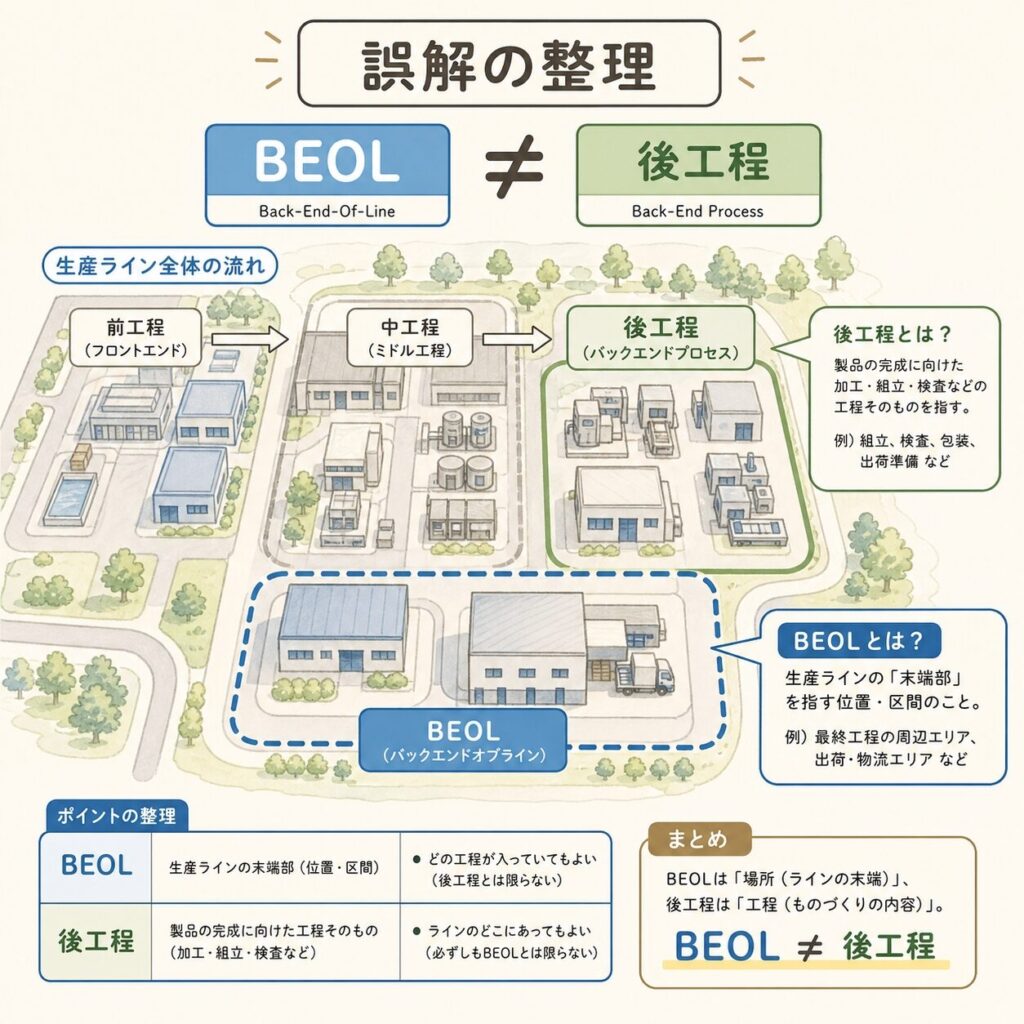

前工程はさらに FEOL(Front End Of Line:トランジスタを作る前半) と BEOL(Back End Of Line:配線を作る後半) に分かれます。「BEOL」と「後工程」は別物なので混同注意。

後工程とは?──ウェーハを「製品」に仕立てる工程

後工程は、英語で Assembly & Test(アセンブリ&テスト) と呼ばれます。前工程で完成した「回路入りのウェーハ」を、1個1個のチップに切り分け、パッケージに組み立て、テストして出荷するまでの工程です。

Outsourced Semiconductor Assembly and Testの略。後工程を専門に請け負う企業のこと。台湾のASE、米Amkorなどが大手。

前工程が「巨大な印刷工場で1枚の大きな紙に何百枚もの絵を印刷する作業」だとすると、後工程は「その紙を1枚ずつ丁寧に切り取って、額縁に入れて、検品して、お客様に届ける作業」です。どちらが欠けてもダメ。

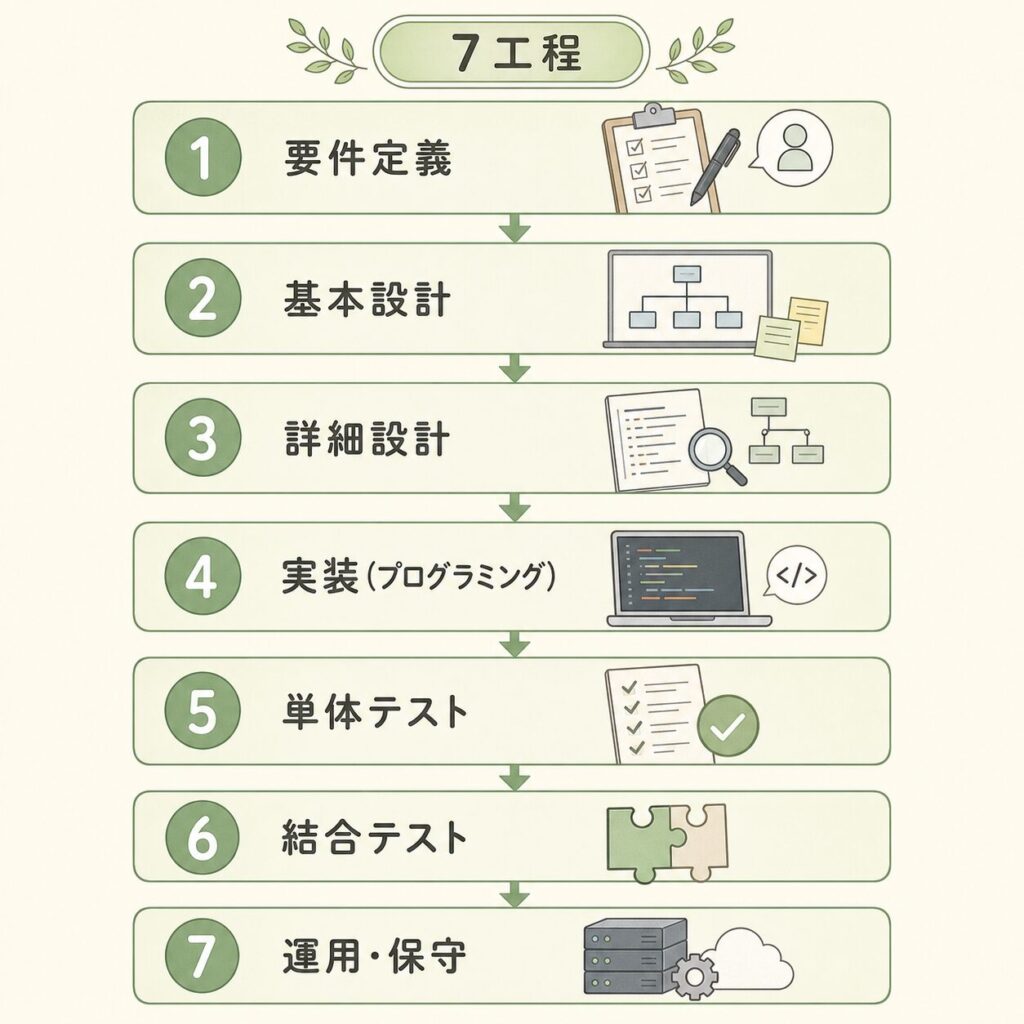

後工程の7つの主要プロセス

後工程は前工程と違って、原則として 「上流から下流に1回流れる」 工程です。前工程のような数百回の繰り返しはありません。

切る前に、ウェーハの状態でチップ1個1個に針を当てて動作確認。不良品をマーキングする。HBM時代に重要性急上昇。

ウェーハの裏面を薄く削って、最終的なチップの薄さに整える。ディスコの主戦場。

ウェーハを1個1個のチップに切り分ける工程。ブレード・レーザー・ステルス・プラズマの4方式。

チップを基板に貼り付け、細い金線などで配線をつなぐ工程。

チップを樹脂で固めて保護。最後の物理保護工程。

出荷前に動作・温度耐性・信頼性を最終確認。アドバンテストとTeradyneが寡占。

AI半導体時代の新しい主役。複数のチップを高密度に統合する技術(CoWoS、HBM、チップレットなど)。

前工程と後工程の違いを「5つの視点」で比較

ここまでの内容を踏まえて、前工程と後工程の決定的な違いを5つの視点で整理します。

| 視点 | 前工程(Fab) | 後工程(OSAT) |

|---|---|---|

| 扱う精度 | ナノメートル(nm) 最先端は2nm |

マイクロメートル(μm) 先端パッケージは一部nm |

| 工程の繰り返し | 9工程を500〜1,000回以上繰り返す | 7工程を原則1回ずつ通過 |

| クリーンルーム | 超清浄(ISO Class 1〜3レベル) | 比較的緩やか |

| 装置1台の価格 | 数十億〜数百億円 EUVは1台数百億円規模 |

数千万〜数億円 |

| 主要プレイヤー | TSMC・Samsung・Intel・Rapidus +装置5強・材料各社 |

ASE・Amkor・JCET + TSMC(先端パッケージ) |

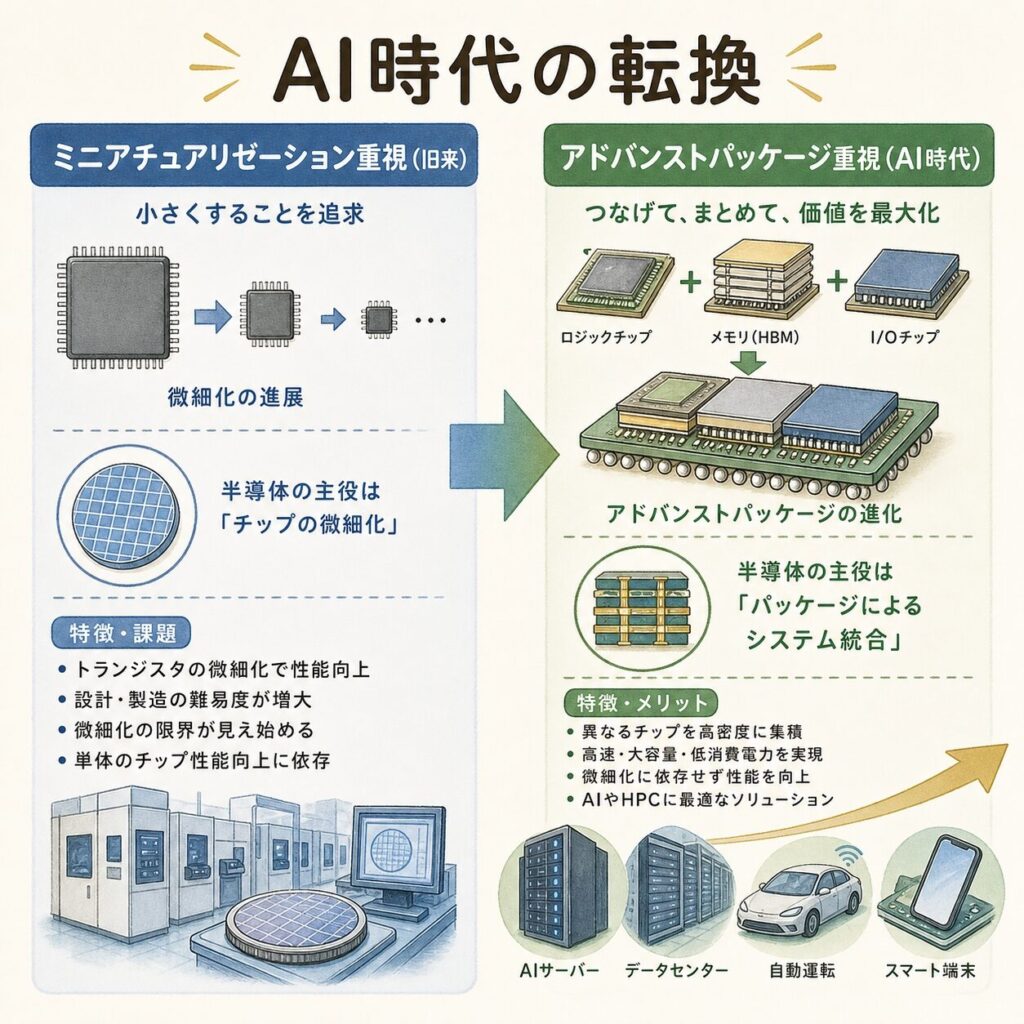

伝統的に「前工程=ハイテクで儲かる」「後工程=労働集約的で利益薄い」と言われてきました。しかしAI時代に入って、後工程の中の「先端パッケージ」だけは前工程レベルの精度・投資額になり、ルールが書き換わりつつあります。後ほど詳しく解説します。

なぜ前工程は「儲かる」と言われるのか?

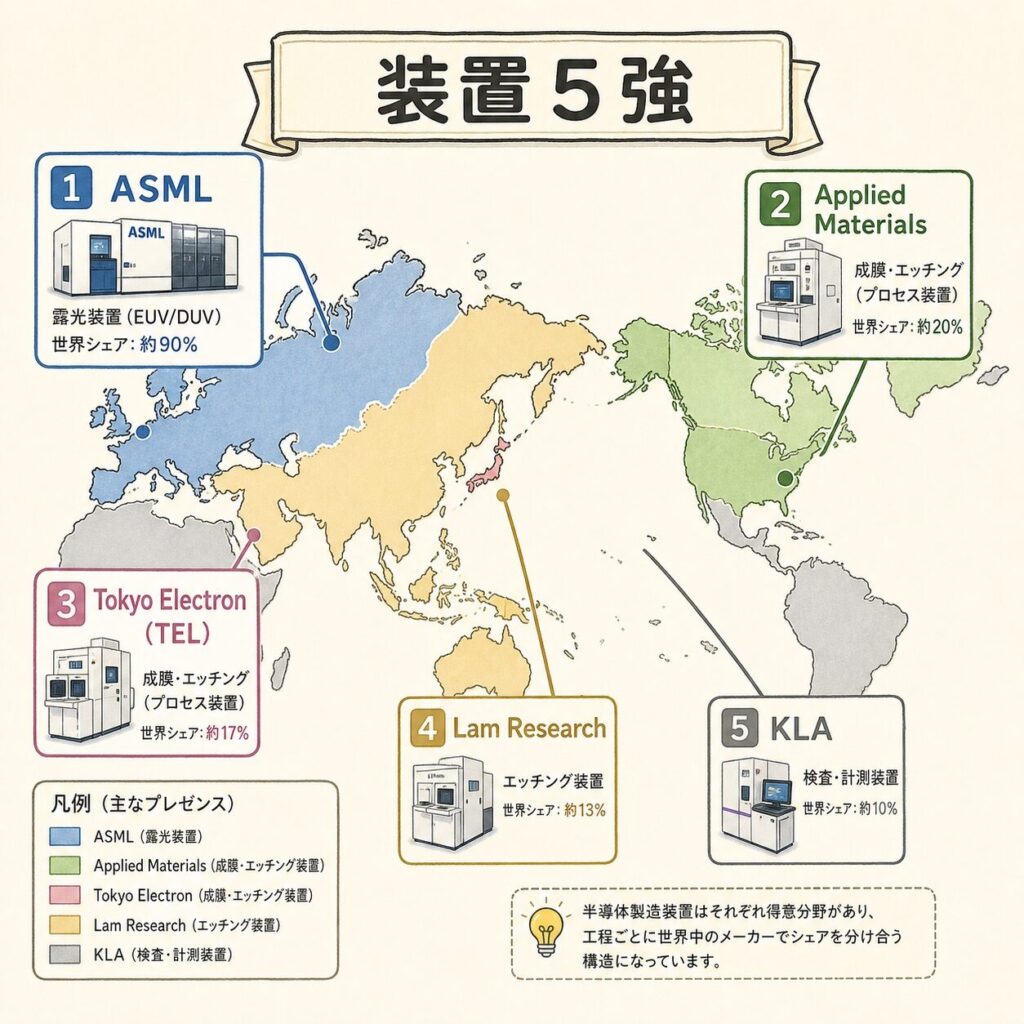

半導体投資をしていると 「前工程の装置メーカーは利益率が高い」「材料メーカーは寡占で安定」 という話をよく聞きます。これは構造的な理由があります。

大半を占める寡占

独占(ASML)

投資規模

前工程の装置と材料は、「他に代わりがいない」状況になっています。EUV露光はASMLしか作れない、シリコンウェーハは信越化学とSUMCOで世界の半分以上、レジスト材料は日本企業が圧倒的シェア。代替不可能性が、高い利益率と価格交渉力を生み出しているのです。

半導体装置メーカー世界5強

(8035)

AI時代の異変──「先端パッケージ」が新たな主役に

半導体業界には、長く 「微細化(前工程)が王者、後工程は脇役」 という常識がありました。しかしAI半導体時代に入り、この構造が急速に変わっています。

前工程の微細化が性能向上の主な手段。後工程は「組み立てるだけ」と見なされ、利益率も低めだった。

後工程の「先端パッケージ」が性能向上の鍵に。CoWoS・HBM・チップレットなどがAI半導体の主戦場となった。

なぜこの変化が起きたのか?理由はシンプルで、微細化のコストが上がりすぎたからです。1チップを単純に小さくするのではなく、「複数のチップを高密度に組み合わせる」方が現実的になった。これがAI時代のチップ設計思想です。

1人の超天才を育てるのが 微細化(前工程)、優秀な専門家チームを連携させるのが 先端パッケージ(後工程)。AI半導体は、後者の「チーム戦」のほうが効率的だと気づいた、というイメージです。

先端パッケージの詳細は、すでに当ブログで複数記事を公開しています。

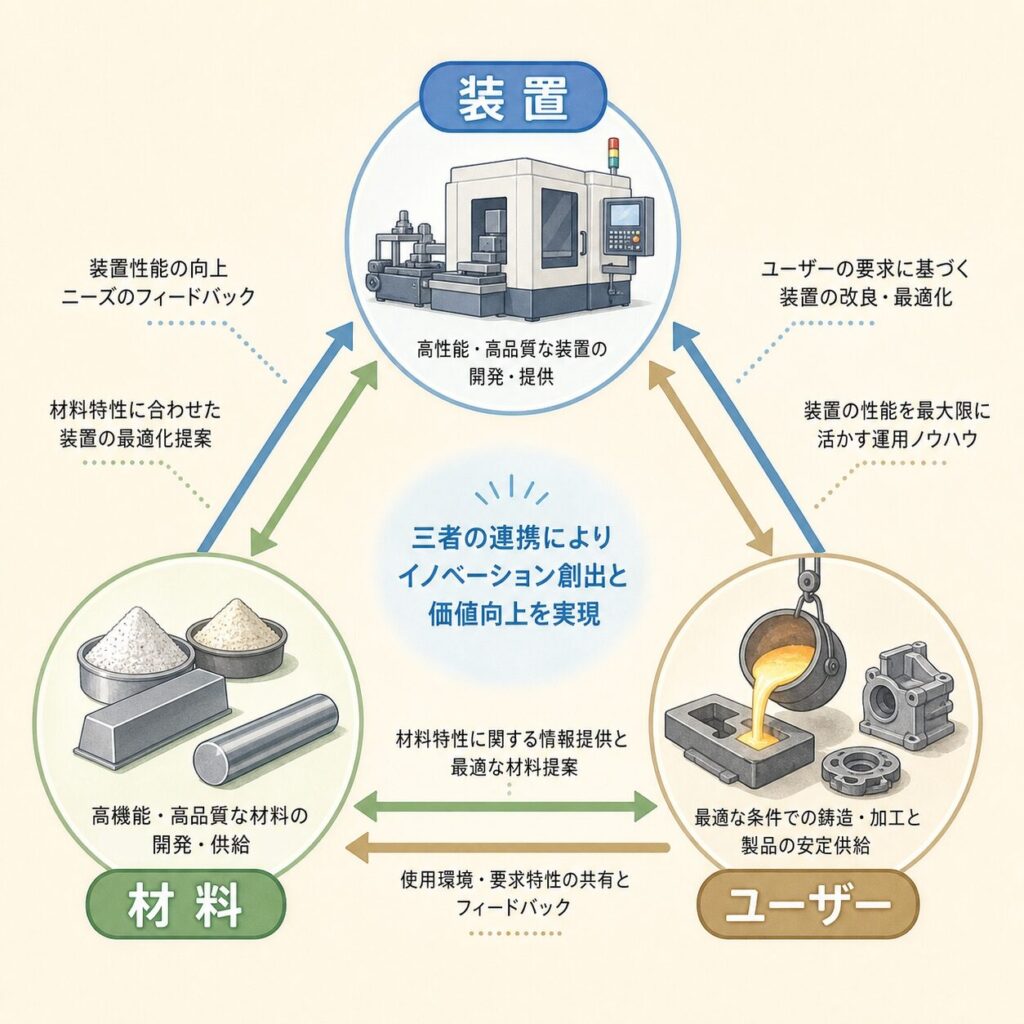

関連企業マップ──「装置」「材料」「使う側」の3面で見る

半導体業界を理解する近道は、「装置メーカー」「材料メーカー」「使う側(ファウンドリ等)」の3面で整理することです。これら3者は 切っても切れない依存関係 にあります。

装置メーカー

プロセスを実行する

機械を作る

- ASML(露光)

- AMAT(成膜・エッチ)

- Lam Research

- 東京エレクトロン(8035)

- KLA(検査)

- アドバンテスト(6857)

- DISCO(6146)

材料メーカー

プロセスで使う

消耗品・素材を作る

- 信越化学(4063)

- SUMCO(3436)

- JSR(4185)

- 東京応化工業(4186)

- HOYA(7741)

- 住友化学(4005)

- レゾナック(4004)

使う側(ユーザー)

装置と材料を使って

実際に半導体を作る

- TSMC(2330.TW)

- Samsung

- Intel(INTC)

- Rapidus(非上場)

- SK Hynix(メモリ)

- Micron(MU)

- キオクシア(285A)

あなたにとっての意味──3層読者別ガイド

半導体株を選ぶときは、まず「装置・材料・使う側」のどこに投資するかを決めること。装置・材料は寡占構造で参入障壁が高く、利益率も高い傾向。一方、使う側(TSMC・Samsung等)は巨額の設備投資を必要とする。AI時代は後工程の先端パッケージ関連企業(DISCO、TOWA、アドバンテスト等)にも注目が集まっています。

あなたの専攻は半導体製造のどこで活きるか?──電気・電子工学はトランジスタ設計や露光・配線、機械工学は装置開発、化学・材料はレジストや薬液、物理学は計測やプラズマ、制御・情報は装置制御や歩留まり解析、と全分野に出番があります。「半導体に関わりたい」という志望は、自分の専門を活かす道が必ず見つかります。

自分の担当外プロセスを理解することが、「全体最適」の視点を生みます。前工程の歩留まりは後工程のテストで初めて判明し、後工程のパッケージ選択は前工程のチップ設計に影響する。プロセス間の依存関係を理解できる技術者は、組織内で希少価値が高い存在になれます。

よくある誤解の整理

全くの別物です。BEOL(Back End Of Line)は前工程の中の後半(配線形成)。後工程(Back-End Process / Assembly & Test)はウェーハを切り分けてからの工程。「Back End」という言葉が両方に使われるので混同されがちです。

AI時代以前の常識です。HBMの3D積層、CoWoSの2.5Dパッケージ、ハイブリッドボンディングなど、現代の先端パッケージは前工程レベルの精度と設備投資が必要です。TSMCは前工程・先端パッケージの両方で世界最強になっています。

「ファウンドリでは負けた」が正確な表現です。装置・材料の領域では日本企業が世界トップクラスのシェアを維持しています。東京エレクトロン、アドバンテスト、DISCO、信越化学、SUMCO、JSR、東京応化工業、HOYA、レーザーテック──いずれも各領域の世界的プレイヤーです。

技術ロードマップ上では 1.4nm、1nm、さらにその先 も研究が進んでいます。ただし「nm表記」はマーケティング上の世代表現であり、実際のトランジスタ寸法とは一致しません。微細化のペースは鈍化していますが、止まったわけではありません。

まとめ──「半導体製造プロセス」という地図を持つこと

半導体製造は、前工程9プロセスと後工程7プロセスの組み合わせです。前工程はナノメートル精度・繰り返し・寡占装置による 「微細化の世界」、後工程はパッケージ化・テストによる 「製品化の世界」。AI時代は、後工程の中の 「先端パッケージ」 が新たな主役として浮上しました。

この地図を持っていれば、これからどんな半導体ニュースを読んでも 「これは前工程の◯◯の話だ」「これは後工程の先端パッケージだ」 と即座に位置づけられます。投資判断・キャリア選択・実務の理解、すべての土台になる視点です。

❓ よくある質問(FAQ)

📚 次に読むべき記事

本記事は「半導体プロセス入門」カテゴリのピラー記事です。以下の順で読むと、業界の全体像が立体的に理解できます。

※ 本記事は「半導体プロセス入門」カテゴリ全体の地図です。

各プロセスの詳細記事は、上記リンクから順に読み進めてください。

コメント