「TSMC」──AI半導体のニュースで最も頻繁に登場する企業のひとつ。しかし、その支配力の構造を正確に理解できていますか?

- TSMCは「ファウンドリ」と聞くけど、何を作っている会社? NVIDIAとの関係は?

- CoWoSの生産能力がAI GPU出荷の「蛇口」と言われる理由がわからない

- 3nm・2nmと言われても、何がすごくて何がボトルネックなのかピンとこない

- NVIDIAがTSMC最大の顧客になったと聞いたが、どういう構造?

- 直近決算で純利益率50%超と聞いたが、なぜこんなに儲かるの?

- TSMCの事業構造──「設計はしない。作るだけ」のファウンドリモデル

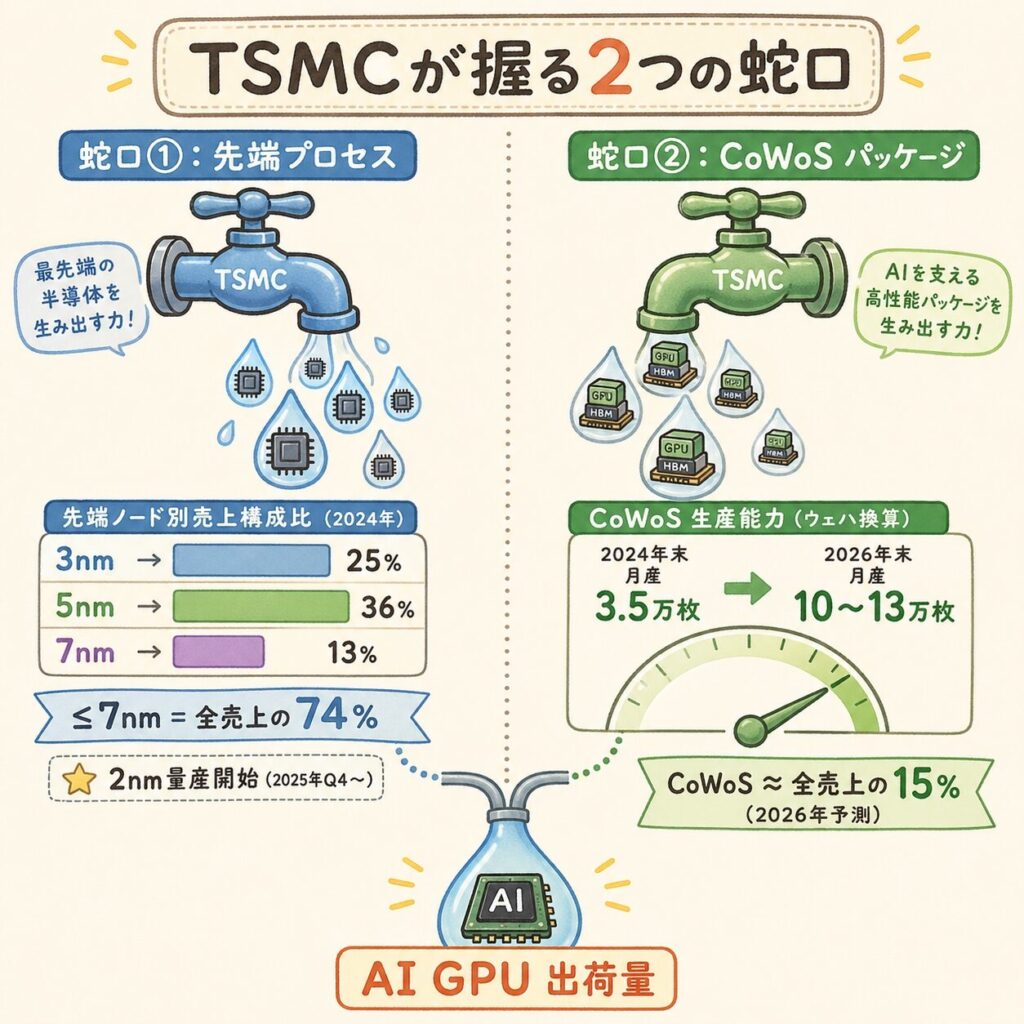

- AI半導体のサプライチェーンでTSMCが握る2つの「蛇口」(先端プロセス+CoWoS)

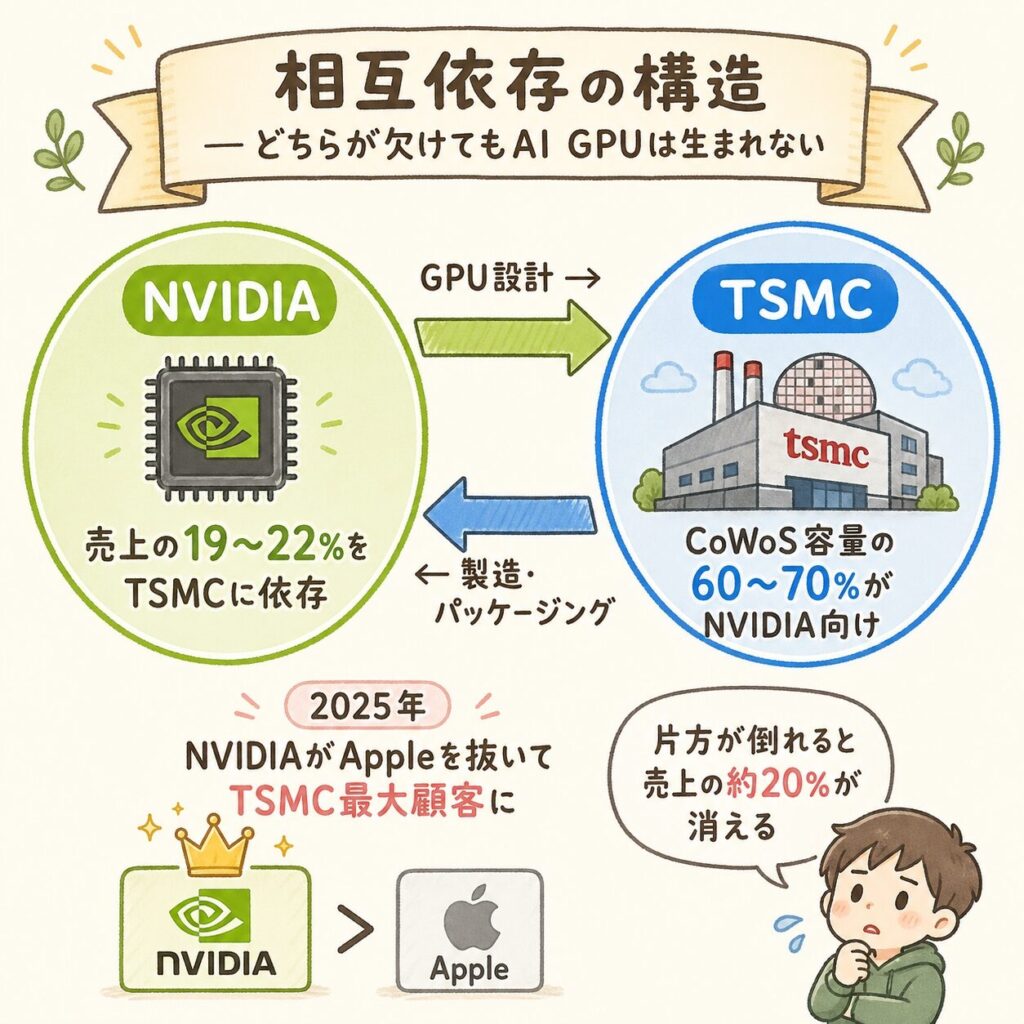

- NVIDIAがTSMC最大の顧客になった構造と依存関係

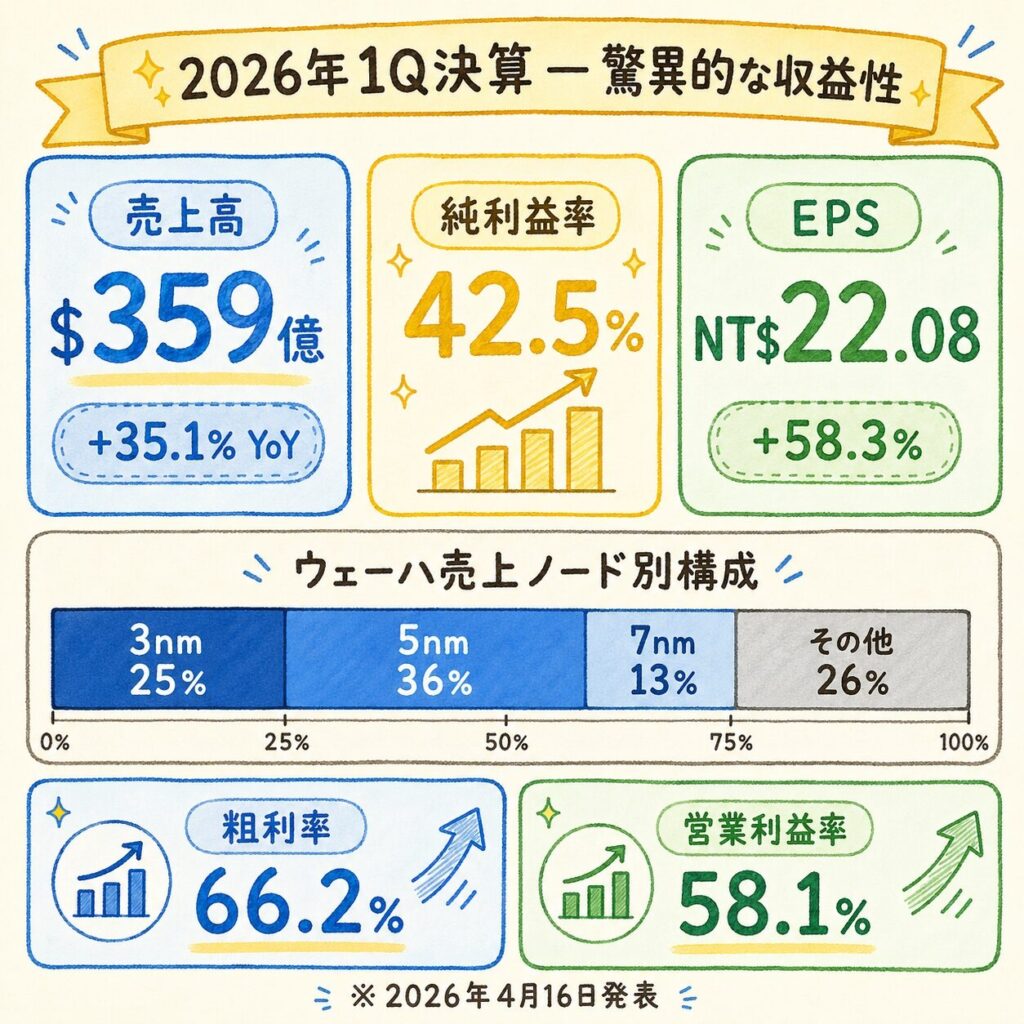

- 1Q2026決算(売上359億ドル・純利益率50.5%・前年比+58.3%増益)の分析

- 2nm量産開始・設備投資520〜560億ドルの意味

- 投資家が見るべきリスクと成長ドライバー

TSMC(台湾積体電路製造、NYSE: TSM)は、世界の先端半導体製造の60%以上を担う「ピュアプレイ・ファウンドリ」です。自社でチップを設計せず、NVIDIA・Apple・AMD等の設計を受託して製造する──この「工場に徹する」モデルで、AI時代に2つの決定的な「蛇口」を握っています。第一に、3nm/2nmの先端プロセス製造。NVIDIAのBlackwell GPU(B200)はTSMCの3nmなしに製造不可能です。第二に、CoWoS先端パッケージング。GPUとHBMを1つに統合するこの技術の生産能力が、世界のAI GPU出荷量を直接制約しています。2026年1Q決算は売上359億ドル(前年比+40.6%)、純利益率50.5%で過去最高を更新。2026年通期売上は前年比30%超の成長を見込み、設備投資は520〜560億ドル。NVIDIAはTSMC売上の推定約19〜22%を占める最大顧客となり、両社の依存関係はAI産業の構造そのものです。

※本記事の業績データは2026年4月16日発表のTSMC 1Q2026決算(SEC提出Form 6-K)に基づいています。株価・業績は記事作成時点(2026年4月25日)の情報です。

TSMCとは?──「設計はしない。作るだけ」の世界最大の半導体工場

🏭 「ピュアプレイ・ファウンドリ」とは何か

TSMC(Taiwan Semiconductor Manufacturing Company、台湾積体電路製造)は、1987年に設立された世界最大の半導体受託製造企業です。自社ブランドのチップは一切作らず、顧客が設計したチップを代わりに製造する「ファウンドリ」に徹しています。

半導体の「製造だけ」を請け負う企業のこと。設計は顧客(NVIDIAやApple等)が行い、ファウンドリはその設計図をもとにシリコンウェーハ上に回路を形成する。自社でチップを設計しない「ピュアプレイ・ファウンドリ」はTSMCが1987年に世界で初めて確立したビジネスモデル。

TSMCは「世界最高の印刷所」です。自分で本(チップ)を書くことはしない。NVIDIAやAppleが書いた原稿(設計図)を受け取り、世界で最も精密な印刷機(製造装置)で本に仕上げる。原稿を書く才能は顧客にある。しかし、どんな素晴らしい原稿も、TSMCの印刷機がなければ本にならない──これがファウンドリモデルの構造です。

出典:顧客数・プロセス数は TSMC 1Q2026 Earnings Release(SEC Filing)

TSMCが握る2つの「蛇口」──先端プロセスとCoWoS

🔧 蛇口①:先端プロセス製造(3nm / 2nm)

NVIDIA Blackwell B200のGPUダイは、TSMCの4nm(N4P)プロセスで製造されています。AppleのM4チップは3nm。世界で3nm以下の先端プロセスを量産できるのは、事実上TSMCとSamsungのみですが、AI GPU向けではTSMCがほぼ独占的な地位にあります。

1Q2026決算では、3nm=売上の25%、5nm=36%、7nm=13%で、7nm以下の先端技術が全ウェーハ売上の74%を占めています(出典:TSMC 1Q2026 SEC Filing)。さらに2nmは2025年Q4に量産を開始済みです(出典:TSMC公式)。

1Q2026 技術ノード別ウェーハ売上構成

7nm以下の先端技術 = 74%

📦 蛇口②:CoWoS先端パッケージング

TSMCはチップの「製造」だけでなく、GPUとHBMを1パッケージに統合する「CoWoS先端パッケージング」も担っています。NVIDIAのH100・B200はすべてTSMCのCoWoSで製造されており、NVIDIAはTSMCのCoWoS生産能力の推定60〜70%を確保しています(出典:Silicon Analysts)。

TSMC CEOのC.C. Wei氏は「CoWoSの生産能力は非常にタイトで、2025年から2026年にかけて完売状態が続いている」と明言しています(出典:Fusion Worldwide)。CoWoSの月産能力は2026年末に10〜12万枚への拡大が計画されていますが、需要は2026年に年間約115万枚に達する見通しで、供給の逼迫は続きます。

蛇口① 先端プロセス

・3nm/2nmの量産が可能

・7nm以下が売上の74%

・NVIDIA B200は4nm(N4P)で製造

・2nm量産は2025年Q4に開始済み

・3nm生産ラインはQ3まで完売

蛇口② CoWoS

・GPU+HBMを1パッケージに統合

・NVIDIAが60〜70%の容量を確保

・月産10〜12万枚へ拡大中(2026年末)

・CoWoS売上はTSMC全体の約15%に

・完売状態が継続(CEO発言)

NVIDIAがGPUを「設計」しても、TSMCが「製造」しなければ製品にならない。さらにTSMCがチップを「製造」しても、CoWoSで「パッケージング」しなければAI GPUとして完成しない。TSMCは「製造」と「パッケージング」の2つの蛇口を同時に握っている──これがAI産業におけるTSMCの支配力の源泉です。

📖 【完全図解】CoWoSとは?NVIDIAのGPUを支える先端パッケージ技術を初心者向けに解説 →

NVIDIAがTSMC最大の顧客に──相互依存の構造

🔗 AppleからNVIDIAへ──最大顧客の交代

TSMCの最大顧客は長年Appleでしたが、2025年にその座がNVIDIAに交代しました。TSMCの2025年事業報告書によると、売上比率10%以上の顧客2社のうち、最大顧客(NVIDIAと推定)が約19%、第2位顧客(Appleと推定)が約17%を占めています(出典:ChosunBiz)。

DIGITIMES Researchの推計では、NVIDIAがTSMCにもたらした収益は2025年に7,269億台湾ドル(約3.3兆円)に達し、前年比2倍以上に急増しています(出典:XenoSpectrum)。

最大顧客=Apple

iPhone・Mac向けSoCが売上の中心。

HPC(高性能計算)部門は全売上の約40%。

最大顧客=NVIDIA

AI GPU(H100/B200等)の急拡大。

HPC部門は全売上の約55%に拡大(出典:JBpress)。

TSMCはNVIDIAなしには売上の2割を失い、NVIDIAはTSMCなしにはGPUを1枚も製造できない。両社は「共依存」の関係にあり、どちらかの問題がもう一方に直接波及します。NVIDIAのGPU需要がTSMCの業績を左右し、TSMCのCoWoS生産能力がNVIDIAの出荷数を律速する──この構造がAI半導体産業の根幹です。

1Q2026決算──売上359億ドル・純利益率50.5%で過去最高

| 項目 | 1Q2026 | 1Q2025 | 前年比 |

|---|---|---|---|

| 売上高 | NT$1兆1,341億 | NT$8,393億 | +35.1% |

| 粗利益率 | 66.2% | 58.8% | +7.4pt |

| 営業利益率 | 58.1% | 48.5% | +9.6pt |

| 純利益 | NT$5,725億 | NT$3,616億 | +58.3% |

| EPS | NT$22.08 | NT$13.94 | +58.3% |

出典:TSMC 1Q2026 Earnings Release(SEC Filing、2026年4月16日)

🔮 2Q2026ガイダンス+通期見通し

2Q2026のガイダンスは売上390〜402億ドル、粗利益率65.5〜67.5%。通期では前年比30%超の売上成長を見込んでいます(出典:CNBC)。設備投資は2026年に520〜560億ドル(前年比最大+40%)と過去最大。そのうち約70〜80%が先端プロセスとCoWoS拡張に充てられます(出典:Data Center Dynamics)。

投資家が見るべきリスク要因

TSMCの製造拠点の大部分は台湾に集中しています。中台関係の緊張が高まった場合、世界の先端半導体供給が一気に途絶えるリスクがあります。TSMCはアリゾナ(米国)・熊本(日本)・ドレスデン(ドイツ)への分散投資を進めていますが、最先端プロセス(2nm以下)は当面台湾中心です。

現在の売上成長の大部分はAI GPU需要に支えられています。AI投資サイクルが調整局面に入った場合、TSMCの業績にも減速が起きる可能性があります。HPC部門が売上の55%を占める構成は、AI需要への集中リスクでもあります。

2026年の設備投資は520〜560億ドルと過去最大。需要が想定を下回った場合、減価償却費の重荷が利益率を圧迫するリスクがあります。特に海外新工場(アリゾナ等)は台湾より製造コストが高いとされています。

米国の対中半導体輸出規制により、TSMCは中国の一部顧客への先端チップ供給が制限されています。規制の拡大は中国向け売上に影響を与え、さらに中国のファウンドリ育成を加速させる可能性もあります。

構造的な成長ドライバー──なぜTSMCは「AIが進化するほど強くなる」のか

TSMCの成長は「AIブームという一過性の追い風」ではありません。半導体の技術進化そのものが、TSMCの製造能力への依存度を高める構造になっているのです。ここでは、その因果関係を5つのドライバーに分解します。

🔗 5つの構造的成長ドライバー(因果関係フロー)

① AIモデルの大規模化 → 先端プロセスの独占的需要

GPT-5、Gemini 2、Llama 4クラスの巨大モデルには数十万〜数百万個のAI GPUが必要です。これらのGPUはすべて3nm/2nmプロセスで製造されますが、量産できるのは世界でTSMCだけ。AIモデルが大きくなるほど、TSMCの先端ラインに注文が集中します。2026年1Qの実績では、≤7nmノードが全ウェーハ売上の74%を占めています。

② HBM積層枚数の増加 → CoWoSパッケージングの工数増大

HBMは8層(HBM3)→ 12層(HBM3E)→ 16層(HBM4)と世代ごとに積層枚数が増えています。積層が増えるとパッケージサイズが大きくなり、CoWoSの加工面積とボンディング工数が増加します。TSMCのCoWoS売上は2026年に全売上の約15%に達する見通しです(出典)。

③ CoWoS容量の拡大 → 設備投資の「量」が利益を押し上げ

TSMCは2024年末の月産約35,000ウェーハから、2026年末には月産100,000〜130,000ウェーハへCoWoS容量を3倍以上に拡張中です(出典)。南科(NanKe)AP8新棟の増設やAP7のSoICラインをCoWoSに転換するなど、工場レベルで構造を変えて対応しています(TMTPost)。それでも2026年の世界需要は年間115.4万ウェーハと予測され、需給はタイトなままです。

④ 2nmノードへの移行 → 参入障壁がさらに上昇

TSMCのN2(2nm)は2025年Q4に量産を開始し、2026年に本格立ち上げ中です(TSMC公式)。ナノシートトランジスタ(GAA)構造を採用し、性能とエネルギー効率がさらに向上。N2Pは2026年後半に量産予定。SamsungのGAA 2nmは歩留まり改善が遅れており、Intel 18Aも量産が限定的。2nm世代でもTSMCの独占的地位が続く構造です。ウェーハ単価は3nm比で30〜50%高いと見られ、売上高の押し上げ要因になります。

⑤ 巨額設備投資 → 競合との格差を「不可逆的に」拡大

TSMCの2026年の設備投資計画は520〜560億ドル(約8.2〜8.8兆円)。前年比32%増です(Yahoo Finance)。このうち70〜80%が先端プロセスに充てられます。Samsung FoundryやIntel Foundryはこの規模の投資を継続できる体力がなく、設備投資の差がそのまま技術世代と生産能力の差として固定化されていきます。

📊 GPU世代が進むほどTSMCの加工工程が増える構造

| GPU世代 | 製造プロセス | HBM世代 | CoWoS方式 | TSMCの関与度 |

|---|---|---|---|---|

| A100(2020) | 7nm | HBM2e(4〜8層) | CoWoS-S | 製造 + パッケージング |

| H100(2022) | 4nm | HBM3(8層) | CoWoS-S | 製造 + パッケージング |

| B200(2024) | 4nm | HBM3E(8〜12層) | CoWoS-L | 製造 + 大型パッケージング |

| Vera Rubin(2026予定) | 3nm/2nm | HBM4(12〜16層) | CoWoS-L(拡大) | 製造 + 大型パッケージ + 2nm独占 |

💡 構造的理解のポイント

上の表を見ると、GPU世代が進むにつれて「TSMCが関与する工程の種類と難易度が増えている」ことがわかります。A100時代は「7nmで製造してCoWoS-Sでパッケージする」だけでしたが、Vera Rubin世代になると「2nmで製造 + HBM4対応の大型CoWoS-Lでパッケージ + 次世代ボンディング技術の適用」と、TSMCなしでは完成しないパッケージの複雑さが格段に増しています。

つまり、NVIDIAのGPUが1世代進化するたびに、TSMCへの依存度と支払う金額が構造的に増える──これがTSMCの「AIに強い」の本質です。

まとめ:TSMCの投資構造

📋 この記事のまとめ

① 事業モデル:TSMCは「ピュアプレイ・ファウンドリ」。自社では設計せず、顧客の設計を受託製造する世界最大の半導体受託製造企業です。

② 2つの「蛇口」:AIチップの供給量を決める2つのボトルネック──先端プロセス(3nm/2nm)とCoWoSパッケージングの両方をTSMCが握っています。≤7nmノードが全ウェーハ売上の74%を占め、CoWoSは全売上の約15%に成長見込み。

③ NVIDIA依存の構造:NVIDIAは2025年にAppleを抜いてTSMCの最大顧客に。売上高の約19〜22%を占め、CoWoS容量の約60〜70%を確保。両社は相互に不可欠な関係です。

④ 直近業績(2026年1Q):売上高359億ドル(前年比+35.1%)、純利益率50.5%、EPS NT$22.08(前年比+58.3%)。粗利率66.2%、営業利益率58.1%と驚異的な収益性。

⑤ 今後の見通し:2026年2Q売上高ガイダンスは390〜402億ドル。2026年通期は前年比+30%超の増収が見込まれ、設備投資は520〜560億ドル(前年比+32%)。

⑥ 成長ドライバー:AIモデル大規模化 → 先端プロセス需要増 → HBM積層枚数増 → CoWoS拡大 → 2nm移行で参入障壁上昇 → 巨額設備投資で格差固定化。すべてがTSMCの売上増と利益率向上に直結する構造です。

⑦ リスク:台湾海峡の地政学リスク・AI需要サイクルの減速・巨額設備投資の回収リスク・米中輸出規制の拡大。

結局こういうことです。TSMCは「世界中のAI半導体を作る工場」です。NVIDIAが設計した最先端GPUも、AppleのAチップも、GoogleのTPUも、AMDのInstinct GPUも──すべてTSMCの工場を通らなければ製品にならない。しかもAI半導体が進化するほど、TSMCでしか作れない先端プロセスとCoWoSパッケージングへの依存が深まる構造です。TSMCは単なる「受託工場」ではなく、AI産業全体の出荷量を律速する「蛇口」なのです。

❓ よくある質問(FAQ)

Q. TSMCの競合はいないのですか?

先端プロセス(≤5nm)ではSamsung FoundryとIntel Foundryが競合ですが、量産実績と歩留まりでTSMCとの差は大きいのが現状です。Samsungは3nmでGAA構造を先行導入しましたが歩留まりが低く、Intelも18A(1.8nm相当)の量産は限定的です。特にCoWoSパッケージングでは実質的にTSMCの独壇場であり、NVIDIAやAMDのハイエンドGPUはすべてTSMCに依存しています。

Q. CoWoSの供給不足はいつ解消されますか?

TSMCはCoWoS容量を2024年末の月産約35,000ウェーハから2026年末に月産100,000〜130,000ウェーハへ約3倍に拡大しています。しかし2026年の世界需要は年間115.4万ウェーハ(前年比+70%)と予測されており、拡張後も需給はタイトなままです。一部ではASE(日月光)やAmkor等のOSAT(後工程専業)がCoWoS互換パッケージングの受託を開始していますが、TSMCの品質と歩留まりに追いつくには時間がかかります。業界アナリストの見方では、少なくとも2027年まではCoWoSがAI GPUの供給ボトルネックであり続けるとされています。

Q. TSMCの日本・米国工場はどんな役割ですか?

日本(熊本・JASM)は22/28nm〜12/16nmの成熟プロセスを担当し、車載・産業用途が中心です。AI向け先端プロセスとは異なりますが、日本の半導体サプライチェーン強化に貢献しています。米国(アリゾナ)では4nm工場が2025年に稼働を開始し、さらに2nm/3nm対応の第2・第3工場が建設中です。米国政府のCHIPS法補助金(最大66億ドル)を受けており、地政学リスクのヘッジと米国顧客(Apple・NVIDIA等)への供給強化が目的です。ただし、最先端のCoWoSパッケージング量産は引き続き台湾が中心です。

📚 次に読むべき記事

半導体実装・HBM

【完全図解】CoWoSとは?NVIDIAのGPUを支える先端パッケージ技術を初心者向けに解説

半導体実装・HBM

【完全図解】HBMとは?GPUの隣にある「AI最重要メモリ」を初心者向けに解説

企業分析

【図解】ディスコの研磨・切断技術がHBM・CoWoSの歩留まりを決める理由

半導体実装・HBM

【完全図解】先端パッケージとは?AIチップの「組み立て方」が変わった理由

半導体実装・HBM

【図解】SK Hynix・Samsung・Micronを比較|HBM市場シェアと投資家が知るべき勢力図

半導体実装・HBM

【図解】CoWoS-S・CoWoS-L・CoWoS-Rの違いとは?3種類を表で徹底比較

⚠️ 免責事項

※この記事は特定銘柄の投資推奨ではありません。AIインフラのサプライチェーン構造を理解するための情報提供を目的としています。投資判断はご自身の責任で行ってください。記事中の情報は作成時点のものであり、最新の業績・株価とは異なる場合があります。

📂 参考データソース(情報取得日:2026年4月25日時点)

- TSMC 2026年1Q決算プレスリリース(SEC Filing):SEC EDGAR

- TSMC 2nm技術ページ:tsmc.com/2nm

- TSMC月次売上高:investor.tsmc.com

- TSMC 2025年年間売上プレスリリース:pr.tsmc.com

- TSMC 2026年設備投資見通し:Yahoo Finance

- CoWoS容量拡張計画:FinancialContent

- CoWoS容量目標引き上げ報道:TMTPost

- CoWoS売上比率・容量配分分析:LinkedIn(Kit Yu)

- CNBC・NVIDIAのCoWoS容量確保報道(2026年4月8日):CNBC

- AI需要・CoWoSボトルネック分析:Fusion Worldwide

- 2nm量産開始報道:TechPowerUp

- TSMC 2026年1Q利益急増報道:CNBC(2026/4/16)

- TSMC売上高推移(年次):Macrotrends

- CoWoSボトルネック記事(Digitimes):DigiTimes(2026/4/10)

コメント