「CoWoSに3種類あるらしいけど、違いがまったくわからない」──そう感じているのは、あなただけではありません。

- CoWoS-S、CoWoS-L、CoWoS-Rのアルファベット1文字の違いが何を意味するのかわからない

- 「シリコンインターポーザー」と「RDLインターポーザー」って何が違うの?

- NVIDIAのBlackwellがCoWoS-Sから「CoWoS-Lに移行した」と聞くけど、なぜ?

- 3種類のなかで、今一番重要なのはどれ?

- 自分が学ぶべき技術・投資で見るべきポイントがどこかわからない

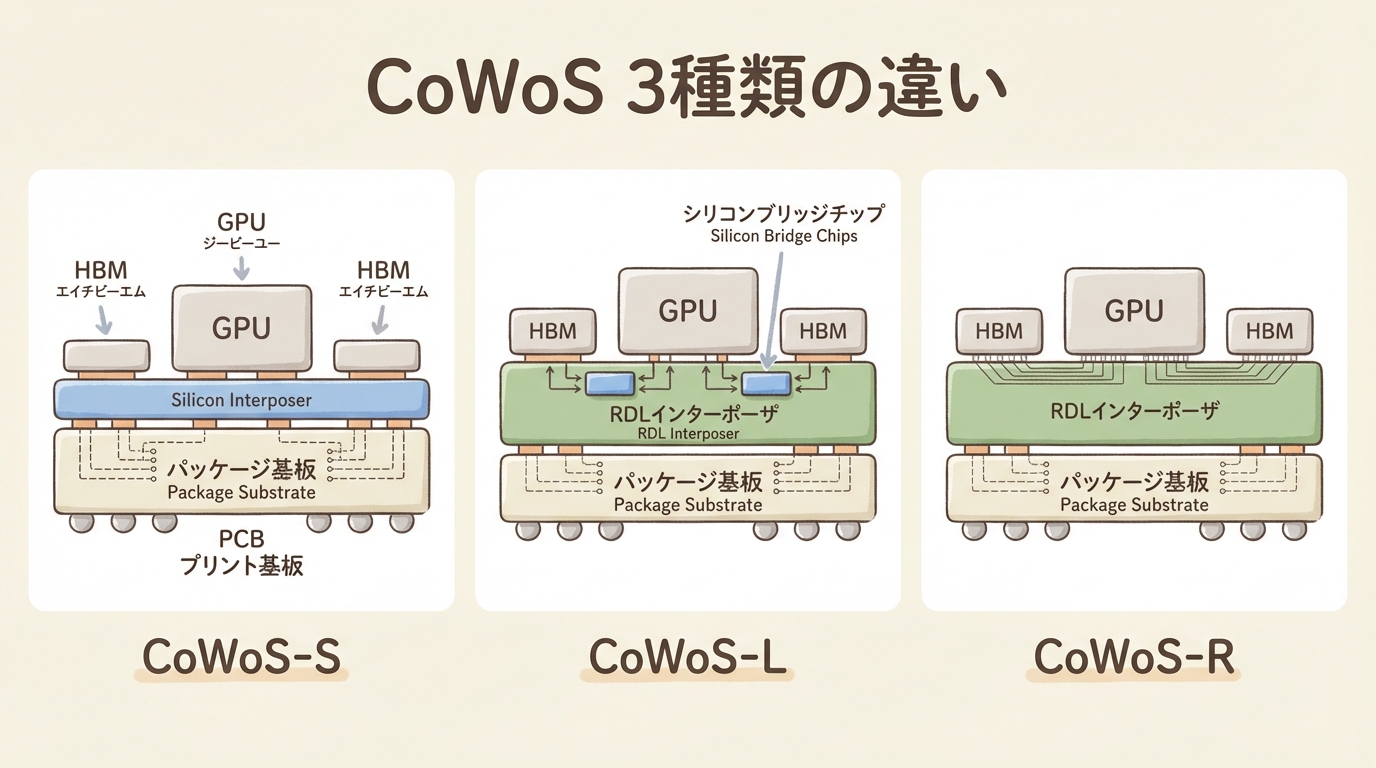

- CoWoS 3種類の違いを決める「たった1つの軸」──インターポーザーの構造

- S・L・Rそれぞれの仕組みを断面図イメージで理解

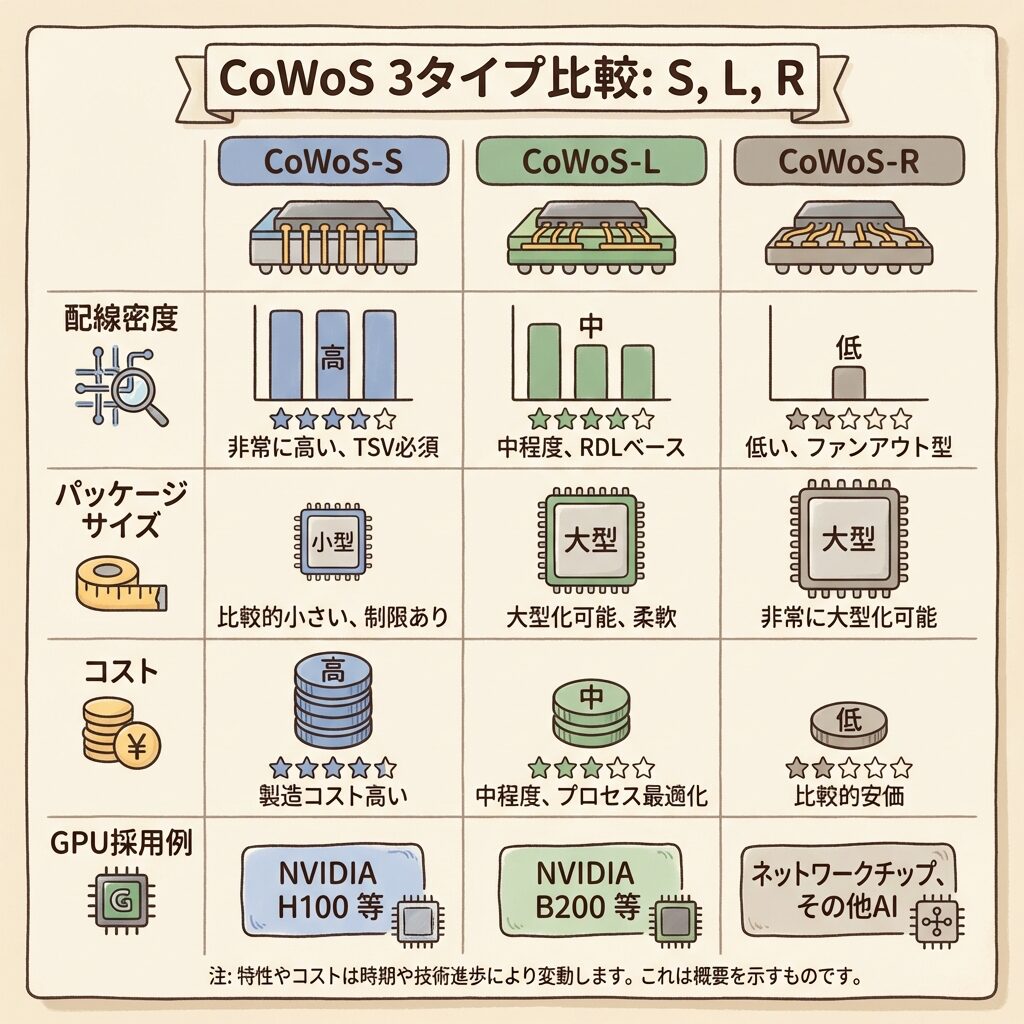

- 8項目の一覧比較表で違いを一目で把握

- なぜNVIDIAがBlackwellでCoWoS-Sを「捨てて」CoWoS-Lを選んだのか

- 電力密度別の「使い分けマップ」で全体像を整理

- 学生・技術者にとってのキャリアへの示唆

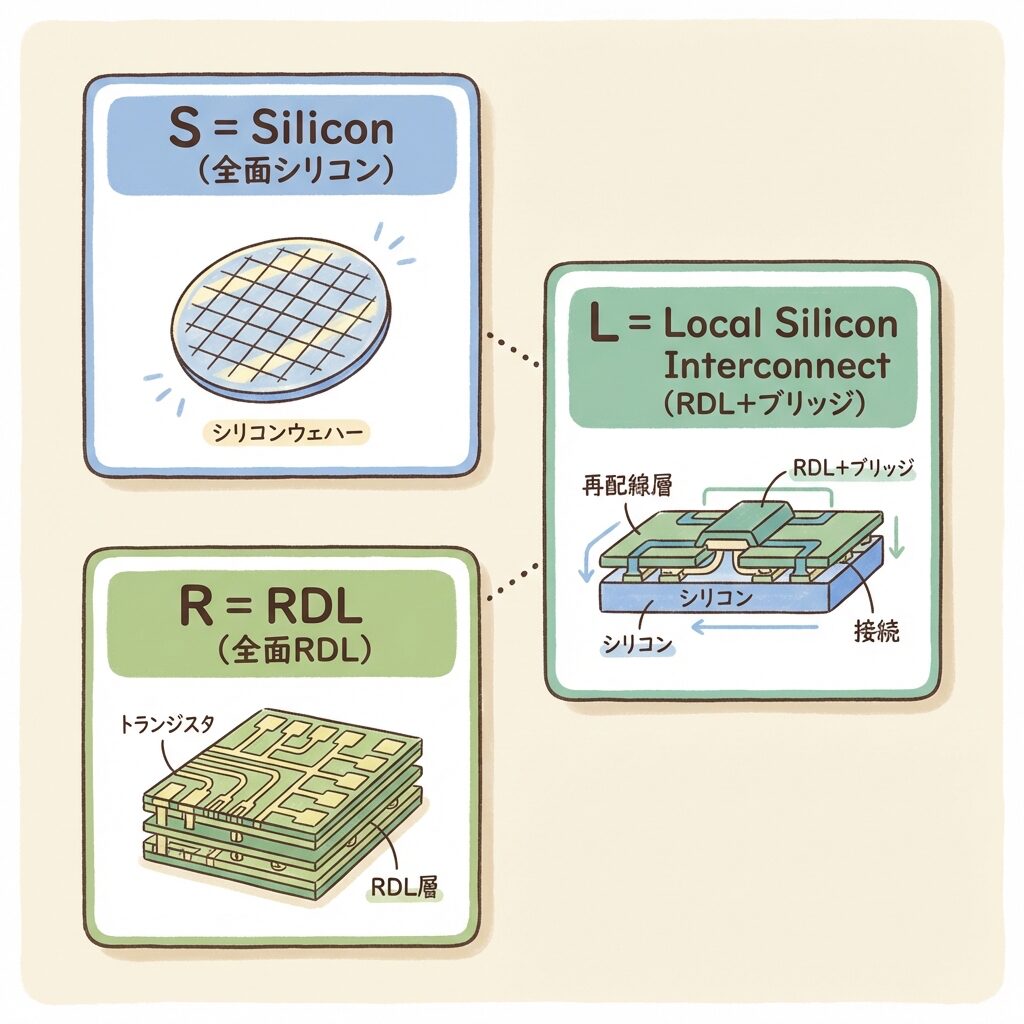

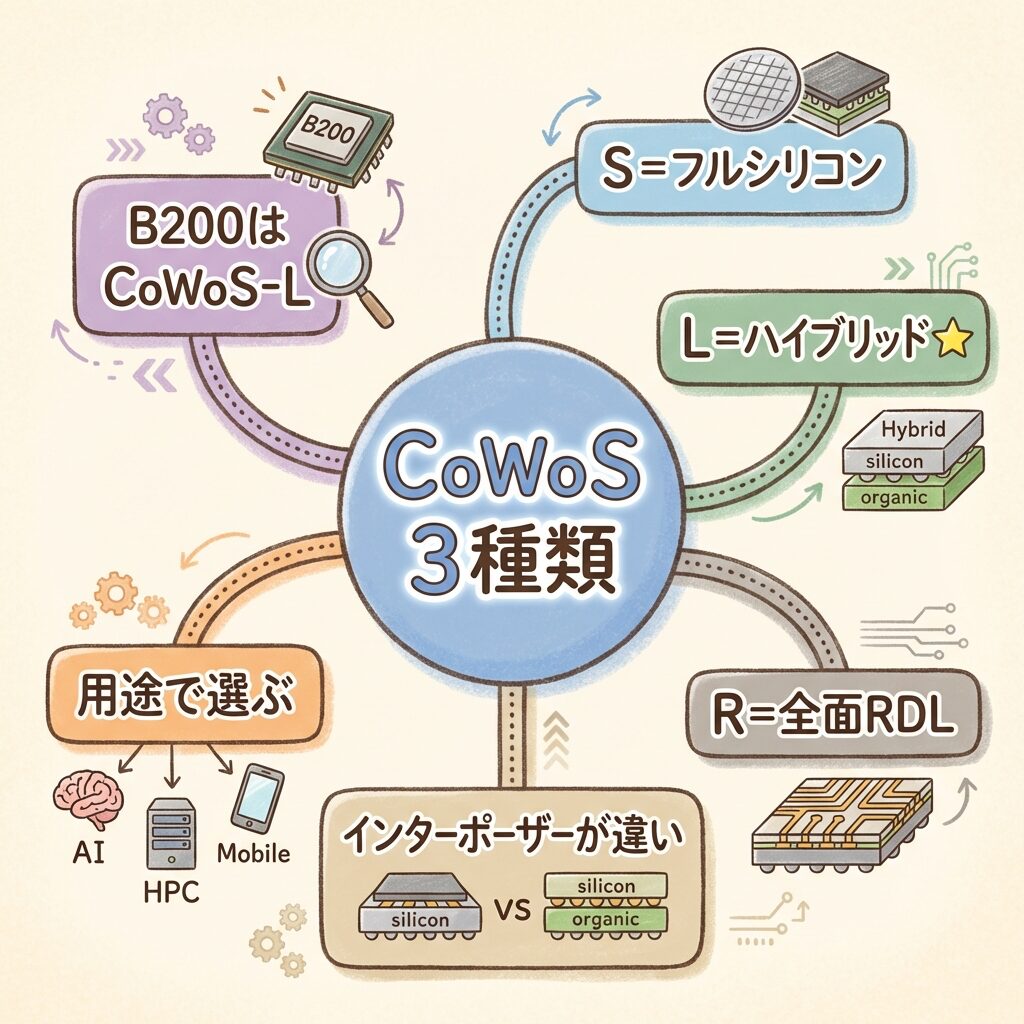

CoWoS-S・CoWoS-L・CoWoS-Rの違いは、「インターポーザー(中間基板)に何を使うか」の1点だけです。CoWoS-Sは全面シリコン(最高の配線密度だがサイズに制限あり)、CoWoS-Rは全面RDL(低コストだが配線密度が低い)、CoWoS-Lはそのハイブリッド(RDL+局所シリコンブリッジで、大型化とコスト、性能を両立)。現在の主流はNVIDIA Blackwell B200が採用したCoWoS-Lであり、TSMC CoWoS-L生産能力の54.6%をCoWoS-Lが占めるに至っています(出典:Yicai Global / DIGITIMES Research)。この記事では、3種類の違いを「構造の断面図」と「8項目の比較表」で整理し、なぜ業界がCoWoS-Lに移行しているのかを構造的に解説します。

前回の記事(CoWoSとは?)では、CoWoSの定義・仕組み・なぜ必要なのかを全体像から解説しました。この記事はその「続編」です。「CoWoSの基本はわかった。じゃあ3種類はどう違うの?」という疑問に、ここで決着をつけましょう。

3種類の違いを決める「たった1つの軸」──インターポーザーの構造

🔑 名前のアルファベットが示す「材料の違い」

CoWoSの3種類は、名前のアルファベットがそのままインターポーザー(中間基板)の構造を表しています。

インターポーザー

のハイブリッド

インターポーザー

3種類の違いは「道路の素材」に似ています。CoWoS-Sは「全面コンクリート舗装の高速道路」──高性能だけど、面積を広げるとコストが跳ね上がる。CoWoS-Rは「全面アスファルトの一般道」──安いけど、高速走行には限界がある。CoWoS-Lは「重要な交差点だけコンクリートで、残りはアスファルト」──コストを抑えつつ、必要な場所だけ高性能を確保するハイブリッドです。

ここで重要なのは、3種類とも「CoWoS」であること。GPUとHBMをインターポーザー上に横並びに配置し、パッケージ基板に搭載する──という基本構造は共通です。違うのは「インターポーザーを何で作るか」だけ。この1点の違いが、配線密度・サイズ制限・コスト・歩留まりすべてを変えるのです。

GPUとHBMなど複数のチップを同一平面上に載せる「中間基板」。チップ同士を超近距離で接続するための高密度配線を備える。CoWoSの性能・コスト・サイズを決める最も重要な構成要素。

📖 【完全図解】CoWoSとは?NVIDIAのGPUを支える先端パッケージ技術を初心者向けに解説 →

この記事は上記ピラー記事の続編です。CoWoSの定義・仕組み・なぜ必要かを先に読むと理解が深まります。

CoWoS-S:全面シリコンインターポーザー──「最高の配線密度」の代償

🔷 CoWoS-Sの構造と特徴

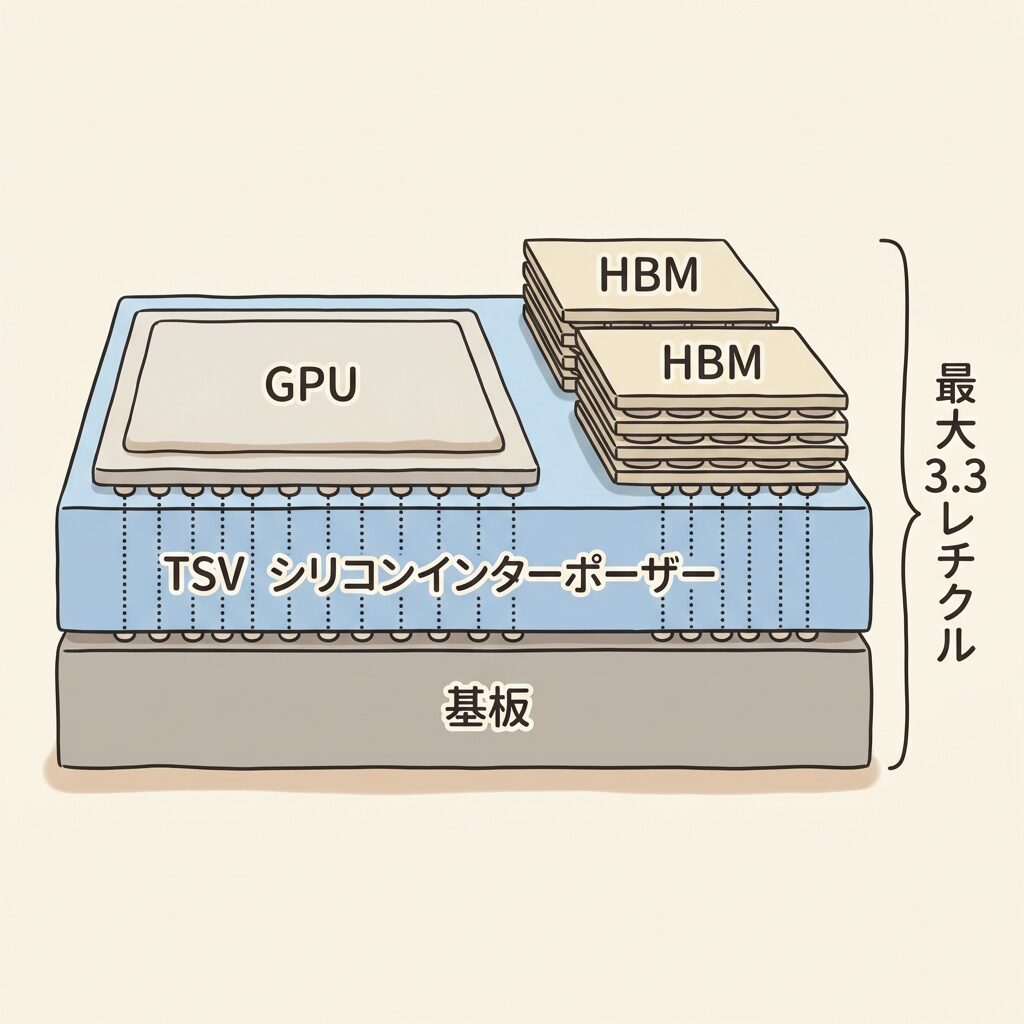

CoWoS-S(S = Silicon)は、CoWoSの最も初期から存在する「元祖」です。インターポーザー全面がシリコン製で、TSV(貫通シリコンビア)を備えた超高密度配線を実現します。NVIDIA A100・H100・H200はすべてこのCoWoS-Sで製造されました。

TSV+サブミクロン配線(最小ピッチ 0.4μm)│ 最大 3.3レチクル(~2,700mm²)

全面がシリコン → 最高密度の配線が可能 → しかしサイズに上限あり

✅ 強み

・最高の配線密度(最小ピッチ 0.4μm)

・TSVによる超高速の表裏接続

・深溝キャパシタ(DTC)を内蔵可能で電源安定化に有利

・長年の量産実績(2012年〜)で製造が成熟

⚠️ 限界

・インターポーザーサイズに上限(最大3.3レチクル ≒ 2,700mm²)

・大型化すると歩留まり(良品率)が急低下

・シリコンは硬くて脆い → 大面積では反りや割れのリスク

・コストが高い(シリコンウェハー加工+TSV工程)

半導体製造でリソグラフィ(回路パターンの転写)に使うマスクの露光範囲のこと。1レチクル ≒ 約800mm²。シリコンインターポーザーはこのレチクルサイズを超えるサイズに広げる技術(マスクスティッチング)を使うが、大きくするほど製造難度とコストが上がる。現在のCoWoS-Sは最大3.3レチクル(約2,700mm²)まで対応(出典:TSMC公式)。

H100(HBM3×5スタック)までは3.3レチクル内に収まっていました。しかしBlackwell B200はGPUダイが2つ+HBM3E×8スタックを搭載する必要があり、3.3レチクルでは物理的に収まりません。ここでCoWoS-Sの「サイズの壁」が顕在化し、CoWoS-Lへの移行が必然となったのです。

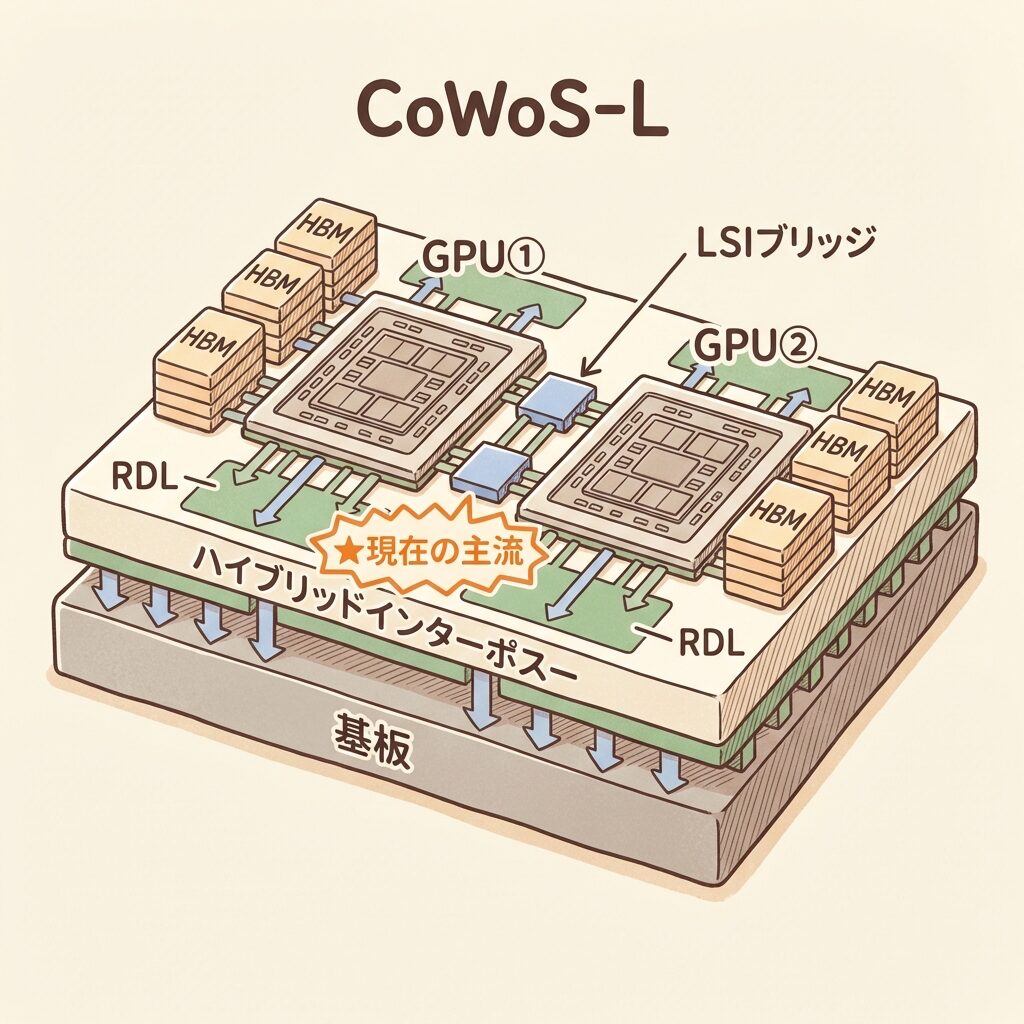

CoWoS-L:RDL+シリコンブリッジの「ハイブリッド」──AI GPUの現在の主流

🔶 CoWoS-Lの構造と特徴

CoWoS-L(L = Local Silicon Interconnect)は、CoWoS-SとCoWoS-Rの「いいとこ取り」をした技術です。インターポーザーの大部分をRDL(有機再配線層)で構成し、チップ間の高速通信が必要な部分だけに小さなシリコンブリッジ(LSI:Local Silicon Interconnect)を埋め込みます。

RDL(安い)+ LSIブリッジ(高速)のハイブリッド → サイズ制限が大幅に緩和

RDLインターポーザーの中に埋め込まれた小さなシリコンチップ。GPU-HBM間やGPU-GPU間など、高速通信が必要な箇所にだけ配置される。CoWoS-Sのシリコンインターポーザーと同等のサブミクロン配線密度を、局所的に実現する「橋渡し」の役割。

有機材料(ポリマー+銅配線)で形成される再配線層。シリコンインターポーザーより配線密度は低い(最小ピッチ約4μm)が、コストが大幅に安く、大面積化が容易。

✅ 強み

・サイズ制限が大幅に緩い(3.3レチクル超に対応)

・必要な箇所だけ高密度配線 → コストと性能を両立

・RDL部分が「緩衝材」になり熱応力に強い

・GPUダイ2つ+HBM8スタックなど、大規模構成に対応

・CoWoS-Sのサブミクロン配線密度をLSI部分で継承

⚠️ 限界

・製造プロセスがCoWoS-Sより複雑(RDL形成+LSI埋込+接合)

・初期の歩留まりがCoWoS-Sの99%に対し約90%と低め(出典:EEWorld)

・量産開始が2024年〜で、製造成熟度はまだ発展途上

・単価はCoWoS-Sより20〜40%高い場合もある(出典:Silicon Analysts)

①サイズ:B200は2つのGPUダイ+8つのHBMスタックを搭載し、CoWoS-Sの3.3レチクルでは物理的に収まらない。CoWoS-Lならサイズ制限が大幅に緩い。

②スケーラビリティ:今後のGPU世代(Vera Rubin等)ではさらにHBMスタック数が増える。CoWoS-Lならインターポーザーを拡張しやすい。

③将来性:TSMCは2026〜2027年に5.5〜9レチクル対応のCoWoS-Lを開発予定。「CoWoS-Lの延長線上」にGPUの未来がある。

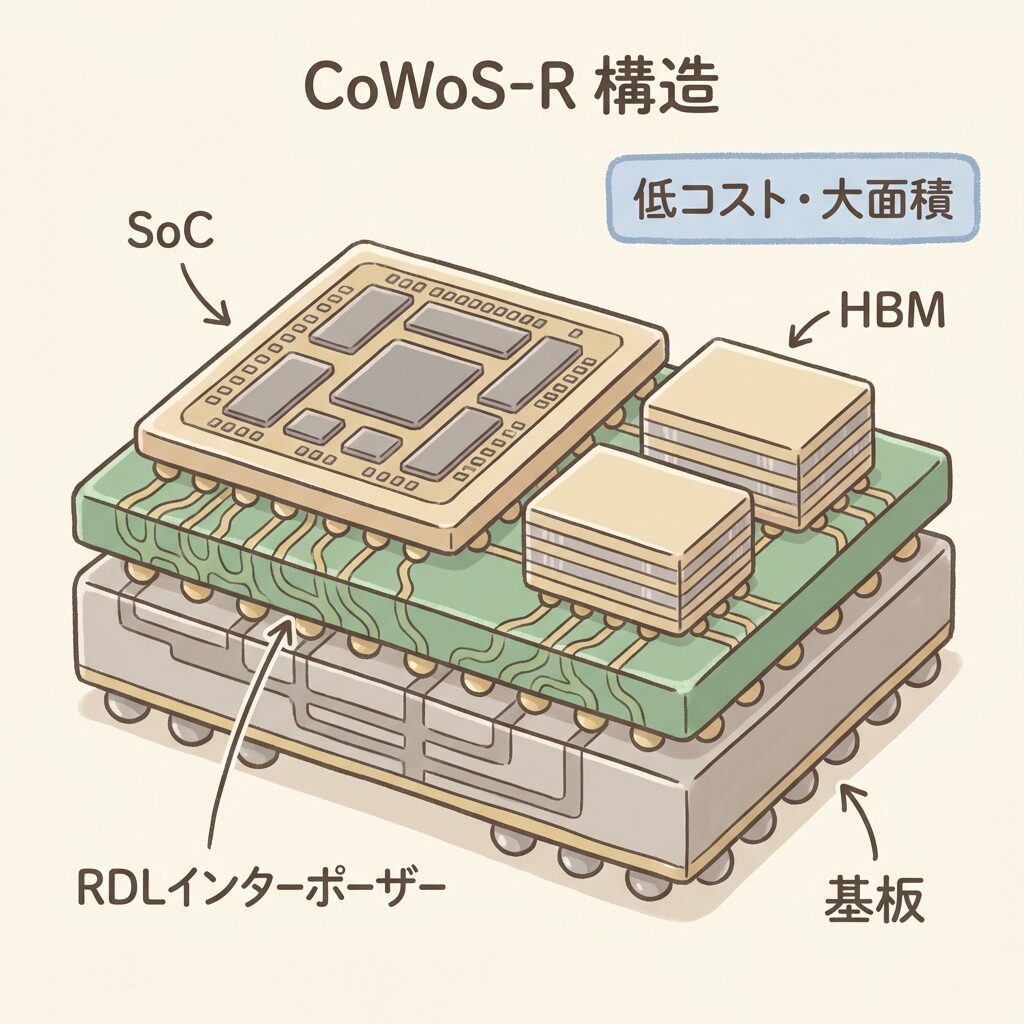

CoWoS-R:全面RDLインターポーザー──「コスト優先」の選択

🔸 CoWoS-Rの構造と特徴

CoWoS-R(R = RDL Interposer)は、シリコンインターポーザーを完全に排除し、全面をRDL(有機再配線層)で構成したCoWoSです。シリコンを使わない分、コストが大幅に下がり、大面積化も容易です。ただし配線密度はCoWoS-SやCoWoS-Lに劣ります。

最大6層銅配線 │ 最小ピッチ 4μm(2μm L/S)│ TSVなし │ サイズ柔軟

全面RDL → 低コスト・柔軟なサイズ → ただし配線密度はCoWoS-S/Lに劣る

TSMCの公式情報によれば、CoWoS-RのRDLインターポーザーは最大6層の銅配線を持ち、最小ピッチは4μm(2μm L/S)です(出典:TSMC公式)。CoWoS-Sのサブミクロン(0.4μm)と比べると約10倍粗い配線ですが、その分コストと歩留まりに大きな優位性があります。

✅ 強み

・コストが最も低い(シリコン不使用+TSV工程なし)

・大面積化が容易(有機材料は柔軟でサイズ制限が緩い)

・RDLが「緩衝材」になり熱膨張率の差を吸収

・高周波信号の伝送損失が低い(GSGSG構造)

⚠️ 限界

・配線密度が最も低い(最小ピッチ 4μm vs CoWoS-Sの0.4μm)

・TSVがないため、裏面接続の自由度が制限される

・超高帯域幅を要求するGPU-HBM間接続には不十分な場合がある

・AI GPUの最先端(H100/B200クラス)には性能的に不向き

【保存版】CoWoS 3種類を8項目で徹底比較

ここまでの内容を1枚の表にまとめます。「CoWoS 3種類の違いを人に説明したい」というときに、この表だけ見返せばOKです。

| 比較項目 | 🔷 CoWoS-S | 🔶 CoWoS-L | 🔸 CoWoS-R |

|---|---|---|---|

| インターポーザー | 全面シリコン+TSV | RDL+局所シリコンブリッジ(LSI)+TIV | 全面RDL(有機再配線層) |

| 最小配線ピッチ | 0.4μm(最高密度) | LSI部分:サブミクロン RDL部分:約4μm |

約4μm(2μm L/S) |

| 最大サイズ | 〜3.3レチクル (約2,700mm²) |

3.3レチクル超対応 (5.5〜9レチクルへ拡大予定) |

3.3レチクル超対応 |

| コスト | 高い | 中〜高い (CoWoS-Sより20〜40%高い場合も) |

最も低い |

| 歩留まり | 小型:約99% 大型化すると低下 |

約90%(初期・改善中) | 高い |

| 量産開始 | 2012年〜(最も成熟) | 2024年〜(急拡大中) | 2020年頃〜 |

| 代表的な採用製品 | NVIDIA A100 / H100 / H200 | NVIDIA B200(Blackwell) 現在のAI GPUの主流 |

Broadcom NWチップ 一部HPC・エッジAI |

| 今後の位置づけ | 縮小傾向 (中小規模GPUでは継続) |

主流として拡大 5.5〜9レチクルへ進化 |

コスト重視の用途で継続 |

出典:配線ピッチ・サイズ情報は TSMC公式、歩留まりは EEWorld、コスト比較は Silicon Analysts、採用製品は Tom’s Hardware を参考に構成

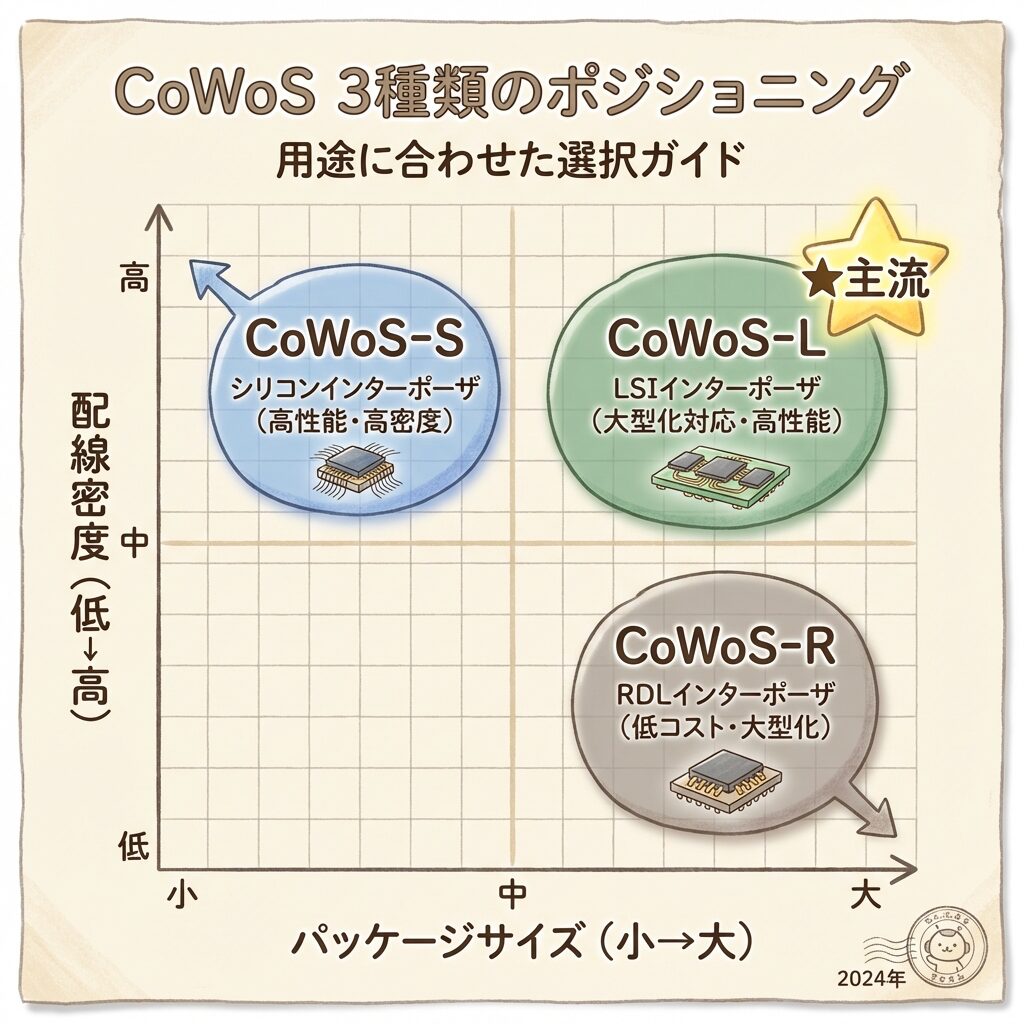

使い分けマップ──「いつ、どのCoWoSを選ぶのか」

🗺️ パッケージサイズと性能要求で決まる

「結局、どの場面でどのCoWoSを使うの?」──答えは、パッケージに求めるサイズと配線密度で決まります。

最高密度が必要+サイズが3.3レチクル内に収まる場合。A100・H100・H200世代。中小規模GPUでは今後も継続。

大型パッケージ+高い配線密度の両方が必要な場合。B200(2ダイ+8HBM)以降の最先端AI GPU。今後5.5〜9レチクルへ拡大。

大面積が必要だが、最高密度の配線は不要な場合。ネットワークASIC・一部のHPC・コスト重視の用途。

CoWoS-Sは「小さいが超精密な金庫」。CoWoS-Lは「大きくて、重要な部分だけ精密な倉庫」。CoWoS-Rは「大きくて安い、一般的な倉庫」。何を収めるかで、どの倉庫を使うかが決まります。最先端のAI GPUを収めるなら、今はCoWoS-L一択です。

【完全図解】GPUサーバーとは?AIサーバーとの違いを初心者向けにやさしく解説 →

CoWoSでパッケージングされたGPUが、どのようなサーバーに組み込まれてAI計算を担うのかを理解できます。

よくある誤解を整理する

| ❌ よくある誤解 | ✅ 実際はこう |

|---|---|

| 「CoWoS-Sが最高性能だから、常にCoWoS-Sが最善」 | CoWoS-Sは配線密度が最高だが、サイズに上限がある。B200のような大規模パッケージは物理的に収まらない。「最高性能=最善」ではなく、用途とサイズに応じた選択が正解。 |

| 「CoWoS-Lのほうが安い」 | 実はCoWoS-Lはプロセスが複雑で、CoWoS-Sより20〜40%高い場合もある。CoWoS-Lが選ばれた理由は「安さ」ではなく、「CoWoS-Sでは収まらない大型パッケージへの対応」。 |

| 「CoWoS-Rは劣った技術」 | CoWoS-Rはコストと大面積化で優れており、ネットワークチップやコスト重視の用途では合理的な選択。すべての半導体が最高密度の配線を必要とするわけではない。 |

| 「CoWoS-Sは廃止される」 | 最先端AI GPUではCoWoS-Lに移行しているが、3.3レチクル以下に収まる中小規模GPUやHPC製品ではCoWoS-Sが引き続き使われる。「廃止」ではなく「用途分化」。 |

| 「3種類はそれぞれ独立した技術」 | 3種類とも「CoWoS」という同じプラットフォームのバリエーション。基本構造(チップを横並びに配置してパッケージ基板に搭載)は共通。違うのはインターポーザーの材料と構造だけ。 |

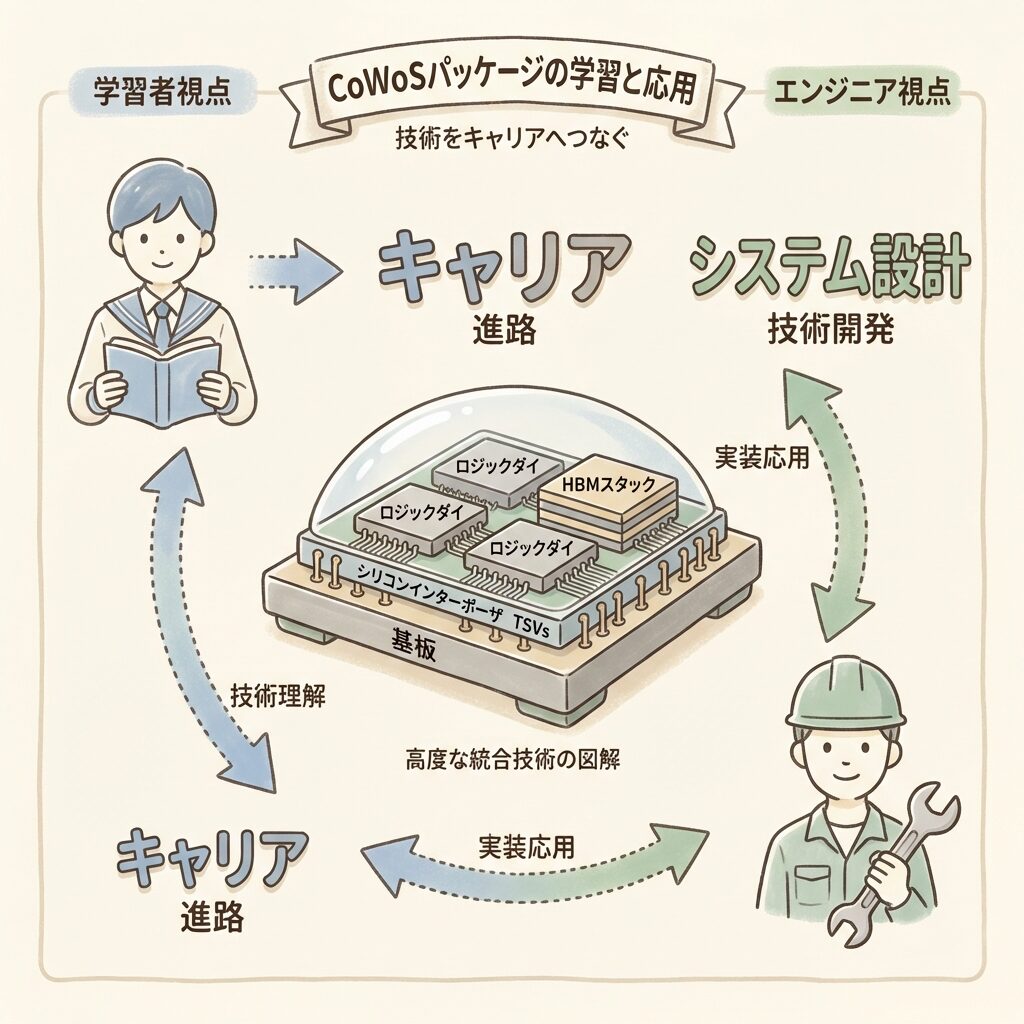

あなたにとっての意味──学生・技術者の視点

CoWoS-S / L / Rの違いを「インターポーザーの材料の違い」と説明できるだけで、面接や研究発表での差別化になります。さらに踏み込むなら、「なぜCoWoS-Sのサイズ制限が3.3レチクルなのか」「LSIブリッジとフルシリコンの配線密度の差がなぜ生まれるのか」を物理的に説明できると、半導体パッケージング分野でのキャリアが開けます。これは情報系だけでなく、材料工学(RDLの有機材料)・精密機械(実装装置)・電気工学(TSV設計)の学生にとっても最前線のテーマです。

CoWoSの種類の違いは、データセンター設計にも波及します。CoWoS-Lの大型パッケージは、ソケット設計・冷却設計・電力供給の前提条件を変えます。B200のCoWoS-Lパッケージは消費電力1,000W超に達し、従来のH100(CoWoS-S)とは冷却要件がまったく異なります。「どのCoWoSで包まれたGPUなのか」を知ることで、システム設計の精度が上がります。

まとめ:CoWoS 3種類の違いの全体像

① 違いは「インターポーザーの材料」の1点:CoWoS-S=全面シリコン、CoWoS-L=RDL+局所シリコンブリッジ、CoWoS-R=全面RDL。

② CoWoS-S:配線密度最高(0.4μm)・最も成熟。ただしサイズ上限3.3レチクル。A100/H100/H200に採用。

③ CoWoS-L:大型化と高密度を両立するハイブリッド。B200(2ダイ+8HBM)が採用。現在の主流であり、5.5〜9レチクルへの拡大が予定。

④ CoWoS-R:最も低コスト。配線密度は低いが大面積化が容易。ネットワークASIC・コスト重視用途で採用。

⑤ BlackwellがCoWoS-Lに移行した理由:2つのGPUダイ+8つのHBMスタックがCoWoS-Sの3.3レチクルに収まらないため。サイズの壁が移行を必然にした。

⑥ 使い分けの基準:3.3レチクル以下→CoWoS-S、3.3レチクル超+高密度→CoWoS-L、大面積+低コスト→CoWoS-R。

⑦ 3種類は「競合」ではなく「用途分化」:すべてCoWoSプラットフォームのバリエーション。どれが「優れている」ではなく、用途で選ぶ。

結局こういうことです。CoWoSの3種類は「優劣」ではなく「トレードオフ」です。配線密度を上げれば→コストとサイズ制限が増える。コストを下げれば→配線密度が落ちる。CoWoS-Lは、このトレードオフの中で「大型化」と「必要十分な性能」を両立する最適解として、AI GPU時代の主流になりました。半導体の進化は「小さくする」だけでなく、「どう組み合わせるか」のパッケージング技術に移りつつあります。

❓ よくある質問(FAQ)

📖 【完全図解】CoWoSとは?NVIDIAのGPUを支える先端パッケージ技術を初心者向けに解説 →

この記事は上記ピラー記事の続編です。CoWoSの定義・仕組み・なぜ必要なのかを先に読むと理解が深まります。

📚 次に読むべき記事

CoWoSで接続される「HBM」の仕組み。3D積層・TSV・市場構造を解説。

CoWoSが「なぜ普通のメモリ接続ではダメなのか」を理解するための前提知識。

CoWoS-Lで大型化したGPUパッケージが、データセンターの冷却・電力設計にどう影響するか。

CoWoS-LのB200パッケージは消費電力1,000W超。冷却問題の構造を理解する。

📩 記事の更新情報を受け取りたい方へ

新しい記事が公開されたら、Xアカウント @shirasusolo でお知らせします。AIインフラの構造を一緒に学んでいきましょう。

コメント