「HBM、CoWoS、先端パッケージ、チップレット……記事はたくさんあるけど、どの順番で読めばいいの?」──そう感じていませんか?

- HBMの記事を読んだけど、CoWoSとの関係がわからない

- 先端パッケージの全体像が掴めないまま個別記事に入ってしまった

- 「DRAMとHBMの違い」と「CoWoS-SとCoWoS-Lの違い」、どっちを先に読めばいいの?

- 投資判断に使いたいけど、知識の土台がバラバラで自信が持てない

- 結局「自分の今のレベルに合った記事」がどれかわからない

- 半導体実装・HBM・CoWoS関連の全記事を1枚の学習マップに整理

- 3つのレベル(入門→構造理解→応用)で「次に何を読むべきか」が明確に

- 各記事の「何がわかるか」と「読む所要時間の目安」

- 目的別ショートカット(投資家向け・学生向け・技術者向け)

- AIデータセンター側の記事とのつながり

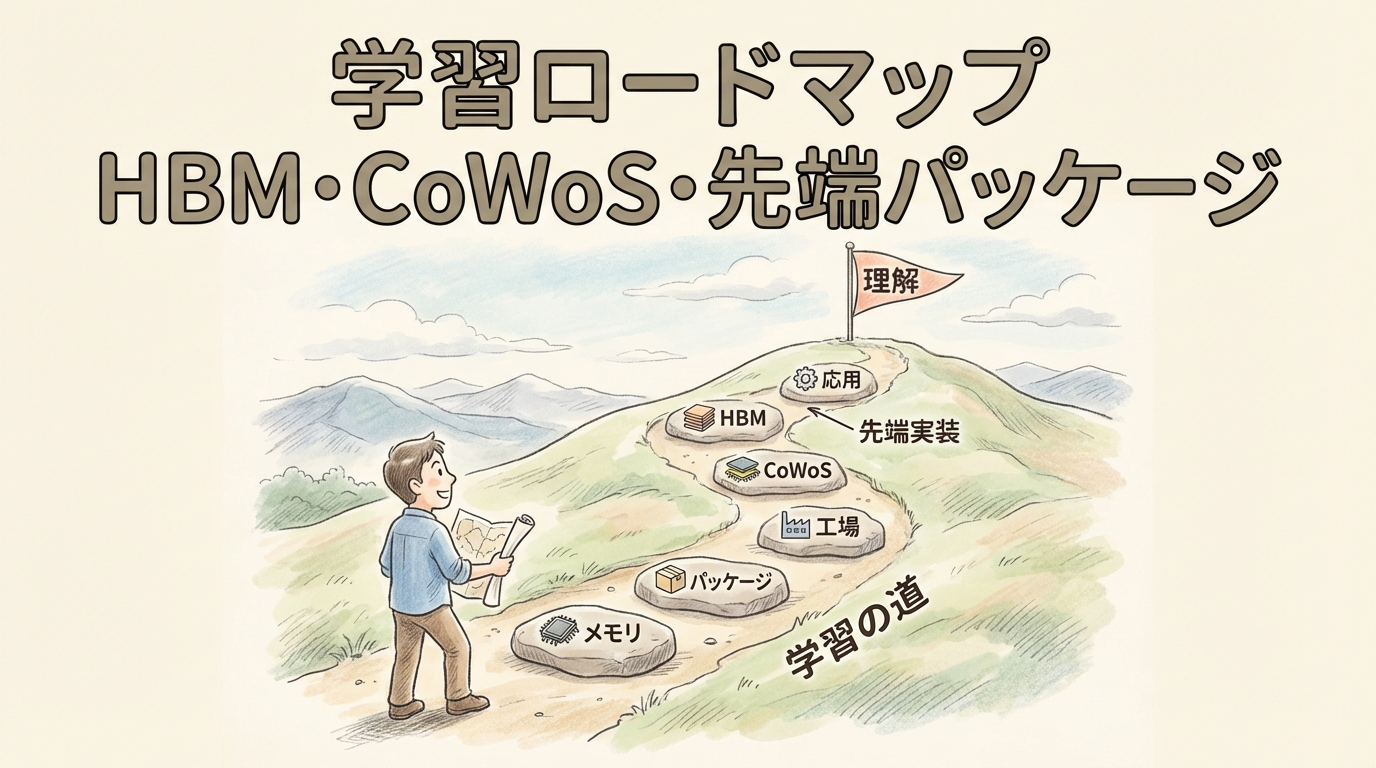

HBM・CoWoS・先端パッケージの知識は、「全体像 → 個別パーツ → つながり → 応用」の順で積み上げるのが最短ルートです。具体的には、まず①先端パッケージの全体像を掴み、次に②HBMとDRAMの違いを理解し、③CoWoSでGPUとHBMがどうつながるかを学び、最後に④市場構造(3社競争・チップレット)に進む──この4ステップで、バラバラだった知識が1本の線でつながります。この記事は、その道順を示す「案内図」です。どこから読んでも大丈夫なように設計していますが、迷ったらこの順番で進めてください。

この記事自体には新しい技術的な内容はありません。すでに公開している記事を「どの順番で読めば最も効率よく理解できるか」を整理した、いわば学習の「地図」です。迷子になったらここに戻ってきてください。

全体マップ──1枚で見る学習の道筋

🗺️ 「先端パッケージ」を頂点にした知識ツリー

半導体実装・HBM関連の全記事は、以下の3つのレベル × 4つのテーマで整理できます。まずこの全体像を頭に入れてから、自分のレベルに合ったステップに進んでください。

Level 1 → 2 → 3の順に進むのが最短ルート。ただし、どこから読んでも記事内で前提知識へのリンクがあるので迷いません。

このロードマップは「山登りのルートマップ」です。Level 1が登山口で基本装備を揃える段階。Level 2が中腹で各ルート(HBMルート・CoWoSルート・チップレットルート)を進む段階。Level 3が山頂で、全体を見渡して「この産業構造のどこに投資チャンスがあるか」を判断する段階。登山口を飛ばして中腹から登ると、途中で迷います。

🟢 Level 1:入門──3記事で「基本の型」を身につける

まったくの初心者は、以下の3記事をこの順番で読んでください。「全体像 → HBMとは何か → DRAMとの違い」という流れで、最小限の労力で基礎が固まります。

「先端パッケージの全体像がわかる」「HBMがDRAMの何倍速いか説明できる」「なぜAIにHBMが必須なのか理由を言える」──この3つができていれば、Level 2に進む準備完了です。

🔵 Level 2:構造理解──3記事で「仕組み」を深掘り

Level 1で基礎を固めたら、次は「GPUとHBMがどうやって1つの製品になるのか」という仕組みを掘り下げます。ここがAI半導体の理解で最も差がつくポイントです。

「CoWoSの3種類の違いを説明できる」「チップレット設計が主流になった理由を構造で語れる」「HBM→CoWoS→GPU→AIデータセンターのつながりが1本の線で見える」──ここまで来れば、産業構造レベルの話ができます。

🟡 Level 3:応用──市場構造と投資判断

技術の仕組みを理解したら、最後は「この知識をどう使うか」のステージです。3社の競争構造を分析し、投資や就職の判断材料にするための応用編です。

「SK Hynixがなぜ強いか、構造で説明できる」「Samsungの巻き返し戦略の論理が読める」「HBMの次世代交代がシェアをどう動かすか仮説を持てる」──技術と産業構造の両方を語れる状態です。投資判断、キャリア判断、業界分析のすべてに使える知識基盤が完成しています。

目的別ショートカット──「全部は読めない」人のための最短ルート

「7記事全部は読む時間がない」という方のために、目的に応じた最短ルートを用意しました。あなたの立場に合わせて、優先度の高い記事から読んでください。

① HBMとは?(なぜHBMが重要か・市場規模)

→ ② CoWoSとは?(ボトルネック構造・TSMCの生産能力制約)

→ ③ SK Hynix・Samsung・Micron比較(3社のシェア・投資の5軸)

① 先端パッケージとは?(全体像・ムーアの法則の減速)

→ ② HBMとは?(3D積層・TSV・メモリウォール)

→ ③ CoWoSとは?(2.5D実装の仕組み)

→ ④ チップレットとは?(設計思想・UCIe・キャリアへの示唆)

① DRAMとHBMの違い(帯域幅・消費電力・実装方式の比較)

→ ② CoWoS-S・L・Rの違い(インフラ設計に直結する冷却・消費電力の前提条件)

→ ③ チップレットとは?(GPUアーキテクチャの変化がシステム設計に与える影響)

AIデータセンター記事とのつながり──「チップの先」を知る

HBM・CoWoS・先端パッケージの知識は、「チップ単体」の話です。しかしチップは単独では動きません。GPUサーバーに組み込まれ、ラックに収容され、電力で動き、冷却で冷やされて、初めてAIが動く──これが「AIデータセンター」の世界です。

半導体パッケージの知識をさらに広げたい方は、以下の記事で「チップの先」にある物理インフラの世界に進んでください。

🏭 AIデータセンター側のおすすめ記事

【保存版】全記事一覧──迷ったらここに戻る

| 順番 | Level | 記事タイトル | 種別 | この記事で得られるもの |

|---|---|---|---|---|

| 1 | 入門 | 先端パッケージとは? | ピラー | 全体の地図。2D/2.5D/3Dの違い。チップレットの概念 |

| 2 | 入門 | HBMとは? | ピラー | HBMの定義・仕組み・世代進化・市場構造 |

| 3 | 入門 | DRAMとHBMの違い | クラスタ | DDR/GDDR/HBMの5視点比較。帯域幅24倍の意味 |

| 4 | 構造 | CoWoSとは? | ピラー | CoWoSの定義・仕組み・3種類・GPU進化との関係・ボトルネック |

| 5 | 構造 | CoWoS-S・L・Rの違い | クラスタ | 3種類の8項目比較。BlackwellがCoWoS-Lを選んだ理由 |

| 6 | 構造 | チップレットとは? | クラスタ | モノリシック vs チップレット。歩留まりの構造。UCIe規格 |

| 7 | 応用 | SK Hynix・Samsung・Micron比較 | クラスタ | 3社シェア・NVIDIA供給関係・HBM4予測・投資5軸 |

❓ よくある質問(FAQ)

📩 記事の更新情報を受け取りたい方へ

新しい記事が公開されたら、Xアカウント @shirasusolo でお知らせします。AIインフラの構造を一緒に学んでいきましょう。

コメント