半導体の「成膜(せいまく)」──ニュースで「KOKUSAI ELECTRICが好調」「ALD装置の需要急増」と聞いても、こんなふうに感じていませんか?

- 「成膜」って、つまり何をしているの?

- CVD・PVD・ALDって名前は聞くけど、違いがわからない

- なぜ半導体に「膜」がたくさん必要なの?

- 装置メーカーがアメリカと日本に集中しているのはなぜ?

- HBMやAI半導体のニュースとどうつながるの?

- 成膜の意味と役割──「膜を積む」とはどういうことか

- なぜ半導体には何十層もの膜が必要なのか

- 4つの主要な成膜方法(熱酸化・CVD・PVD・ALD)の違い

- 成膜装置の世界シェアと日本企業の強み

- 投資家・学生・技術者にとっての意味

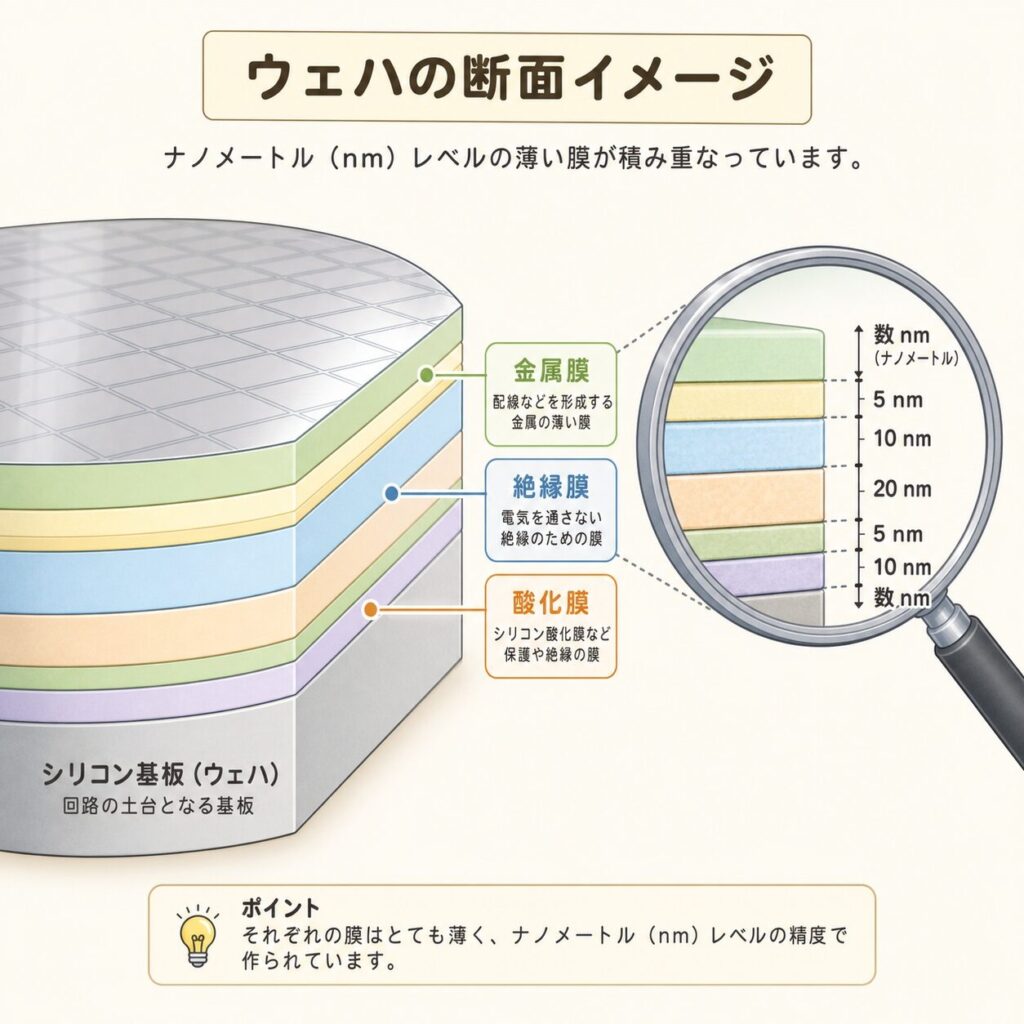

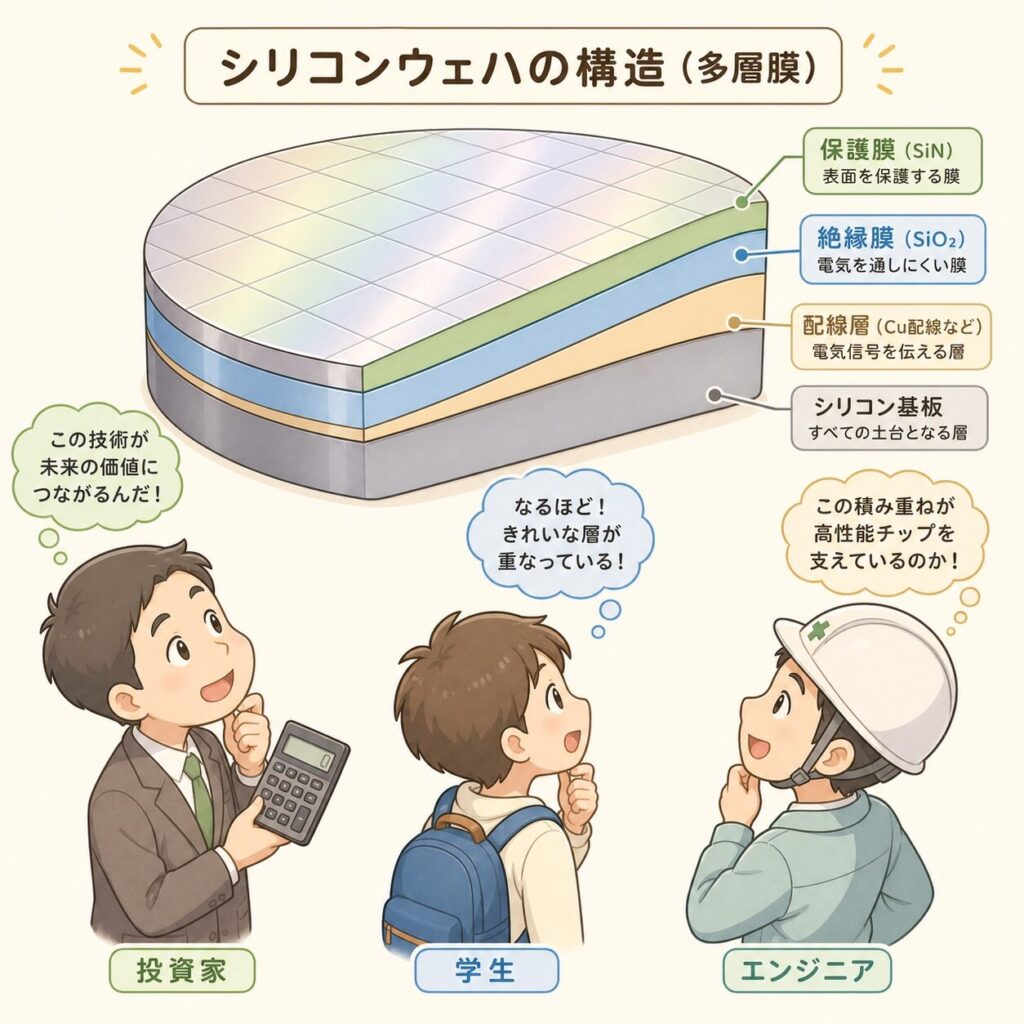

成膜とは、シリコンウェーハの表面に厚さ数nm〜数百nmの極薄い膜を、何層も積み重ねていく工程です。1枚のチップには数十〜100層以上の膜が積まれます。膜の役割は「電気を通す(金属配線)」「電気を遮る(絶縁膜)」「他の層を守る(保護膜)」など多種多様。代表的な成膜方法は熱酸化・CVD・PVD・ALDの4つで、目的と精度によって使い分けます。装置メーカーはApplied Materials(AMAT)・Lam Research・東京エレクトロン・KOKUSAI ELECTRICの4社で世界市場の大部分を占める寡占構造です。AI半導体の進化(GAAトランジスタ・3D NAND・HBM)が、ALDのような「原子1層ずつ積む技術」の需要を構造的に押し上げています。

成膜とは?──「ウェーハに膜を積み重ねる」工程

📦 一言でいうと「ウェーハの上に極薄い膜を作る作業」

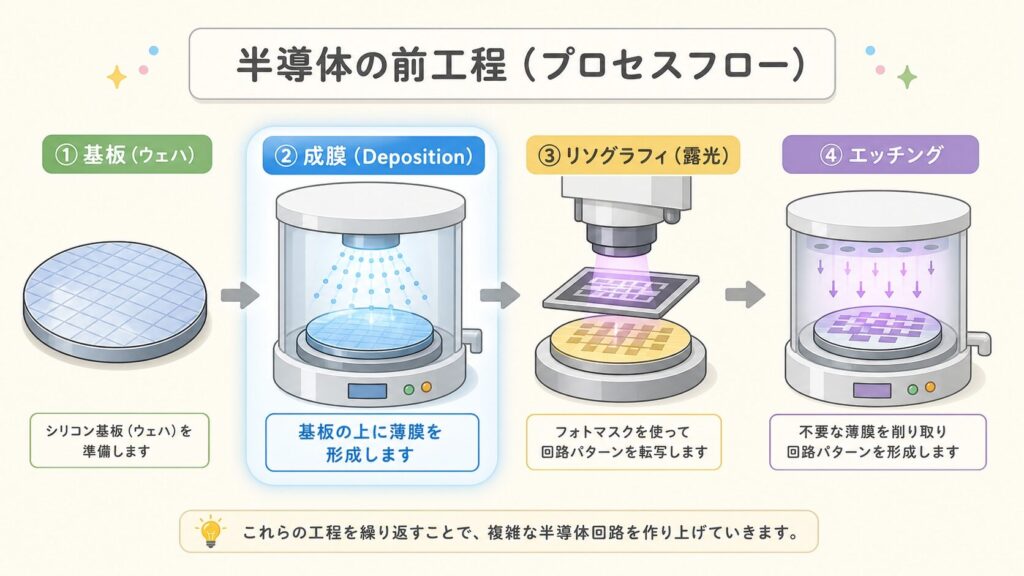

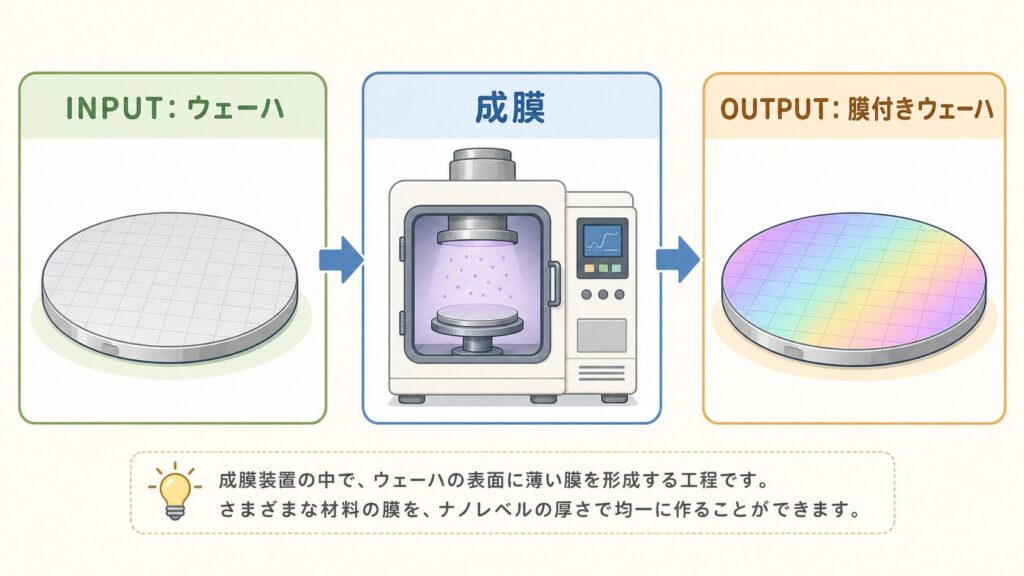

成膜(せいまく / Deposition:デポジション)とは、シリコンウェーハの表面に、厚さ数nm〜数百nmの極薄い膜を作る工程のことです。半導体製造の「前工程」に分類される、なくてはならない基本工程の1つです。

ここでいう「膜」は、私たちが普段イメージする「ラップ」や「シール」とはまったく違います。半導体の膜は原子レベルで薄く、原子レベルで均一でなければなりません。膜の厚さ・成分・むらが、最終的なチップの性能をすべて決めてしまうからです。

成膜は「超精密なミルフィーユ作り」です。1枚1枚のクリームと生地を、原子レベルの厚さで、ウェーハ全面にむらなく重ねていく。1層でも厚すぎたり薄すぎたりすると、ミルフィーユ全体が崩れて食べられなくなります。半導体も同じで、膜が1層でも不均一だとチップが動きません。

シリコンを薄く円盤状に切り出した、半導体製造の出発点となる「素材」。直径300mmのウェーハ1枚から、数百個のチップが作られる。CDのような銀色の円盤をイメージするとわかりやすい。

1nm(ナノメートル)=10億分の1メートル。髪の毛の太さ(約80,000nm)の1万分の1。半導体の膜は、この単位で厚さを管理する。

成膜工程の役割を1枚で理解する

成膜工程は、何を受け取り、何をして、何を次に渡すのか。これを1枚の図で押さえれば、半導体製造の流れの中での成膜の位置づけが見えてきます。

ポイントは、成膜は1回では終わらないこと。ウェーハは「成膜 → 露光 → エッチング → 洗浄 → 成膜 → ……」というサイクルを何十回も繰り返し、最終的に何十層もの膜が積み重なった状態になります。

なぜ「膜」を何十層も積み重ねるのか?

🏗️ チップは「立体的な街」のような構造

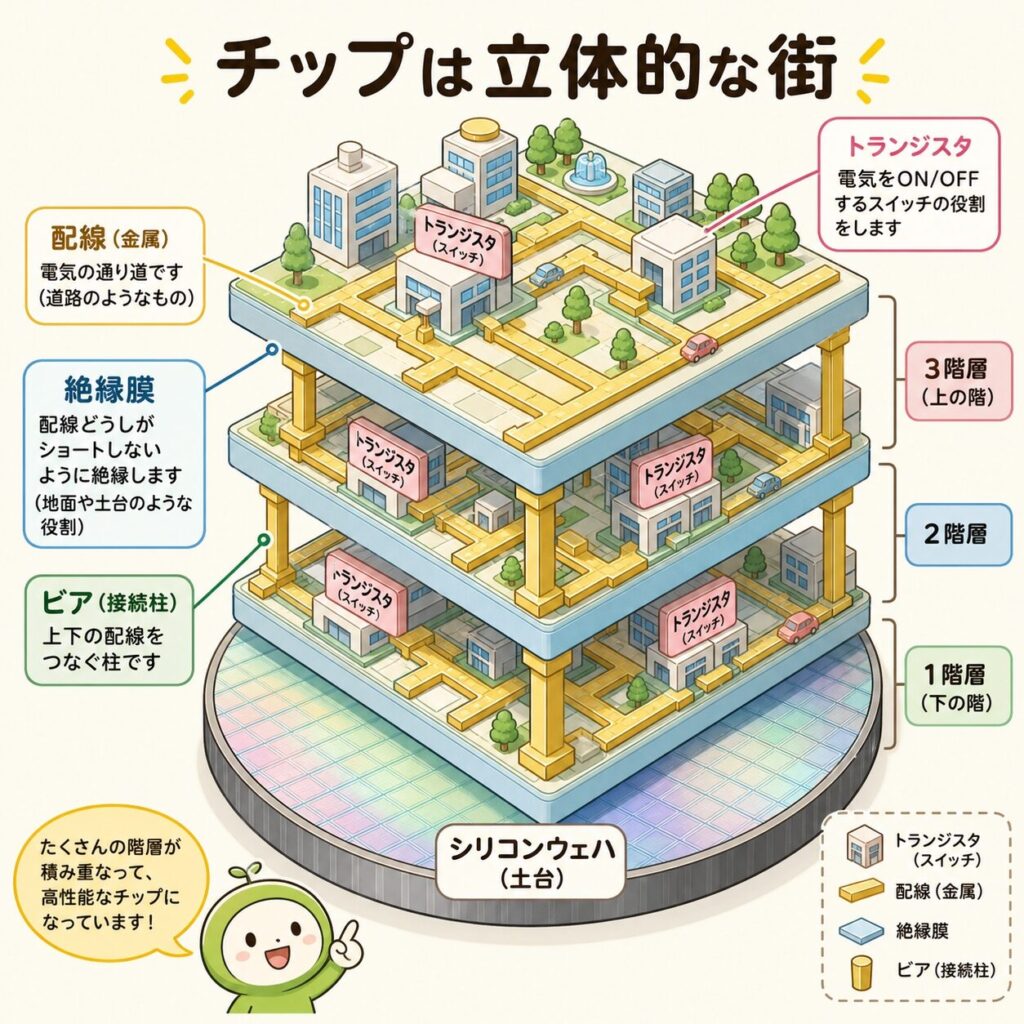

半導体チップの中身は、私たちが想像する「平面」ではありません。建物が密集した立体的な都市のようなものです。膜の役割は、この都市を構成する素材になります。

チップを「超ミニチュアの都市」だと思ってください。電気が流れる金属配線は「道路」、電気を遮断する絶縁膜は「土の地盤」、特殊な機能を持つゲート酸化膜は「信号機の制御装置」です。建物(トランジスタ)と、それをつなぐ配線(メタル層)が、絶縁膜で隔てられながら何階建てにも積み上がっています。

🎨 膜には「3つの役割」がある

最先端のロジックチップでは、金属配線だけで10〜15層、絶縁膜・機能膜まで含めると合計で数十〜100層に達します。これらすべてを、原子レベルの精度で1層ずつ積んでいくのが成膜工程です。

チップに何十層も膜が必要なのは、限られた面積で性能を上げるためです。土地が足りないなら高層ビルを建てる──これと同じ発想で、半導体は「縦方向に積む」ことで集積度を上げてきました。3D NANDメモリでは200層以上を積む製品も登場しており、成膜の重要性は年々高まっています。

成膜の4つの方法──熱酸化・CVD・PVD・ALD

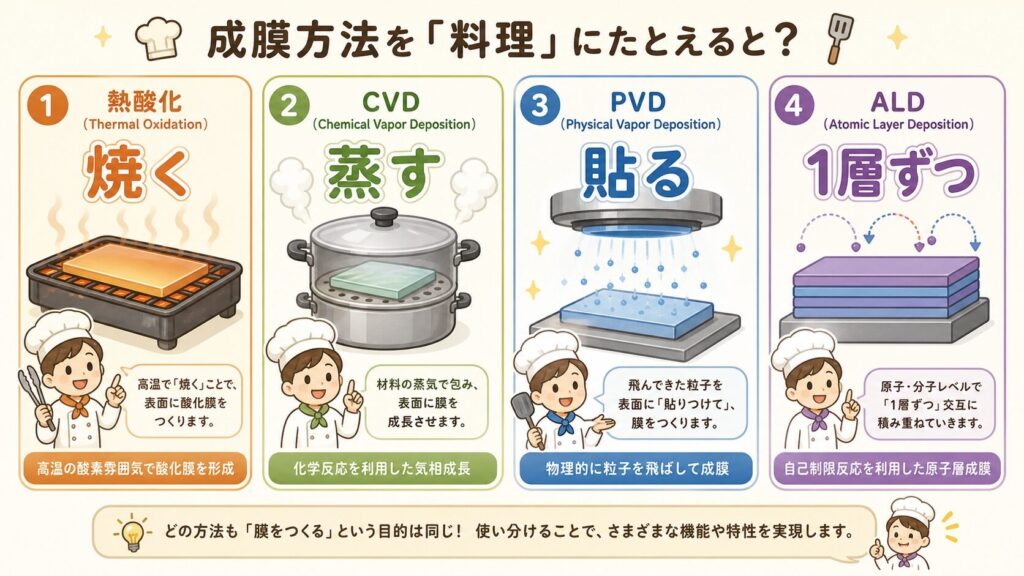

🍳 「料理の調理法」のように使い分ける

ひとくちに「成膜」と言っても、方法は1つではありません。作りたい膜の種類・厚さ・精度によって、4つの代表的な方法を使い分けます。

料理に「焼く」「煮る」「蒸す」「揚げる」があるように、成膜にも熱酸化・CVD・PVD・ALDという4つの調理法があります。それぞれ得意な「料理(膜)」が違うのです。

① 熱酸化

例えるなら:「焼く」

シリコンを高温の酸素にさらして、表面を「焦がす」ように酸化膜(SiO₂)を作る。最も古典的で、品質が高い。

② CVD

例えるなら:「蒸す」

原料ガスを化学反応させて膜を作る。色んな種類の膜を厚く・速く作れる。半導体成膜の主力。

③ PVD

例えるなら:「貼り付ける」

金属の塊を物理的に弾き飛ばし、ウェーハに付着させる。金属配線の主力。スパッタともいう。

④ ALD

例えるなら:「1層ずつ手作業で塗る」

原子1層ずつ膜を作る超精密技術。先端プロセス(GAA・3D NAND)で需要急増。

それぞれの詳細は、シリーズの個別記事で深掘りします。まずは「4つの方法があり、目的によって使い分ける」というイメージだけ持っておけばOKです。

4つの成膜方法を5項目で比較

4つの方法を、初心者にも比較しやすい5つの観点でまとめました。詳しい仕組みは個別記事で解説しますが、この表を頭に入れておけば、シリーズ全体が読みやすくなります。

| 比較項目 | 🔥 熱酸化 | 💨 CVD | 💥 PVD | 🧬 ALD |

|---|---|---|---|---|

| 仕組み | 高温で 表面を酸化 |

ガスの 化学反応 |

物理的に 叩きつける |

原子1層ずつ 順番に付ける |

| 主な膜 | SiO₂ (絶縁膜) |

SiO₂、SiN、 多結晶Si など |

金属膜 (Cu、Ti、Al) |

High-k膜、 バリア膜など |

| 膜の厚さ | 数nm〜数百nm | 数nm〜数μm (厚膜OK) |

数nm〜数百nm | 原子レベル 〜数十nm |

| スピード | 遅い | 速い | 速い | 非常に遅い |

| 精度 | 非常に高い | 高い | 中程度 | 究極 |

「ALDが一番精密だから、ALDだけ使えばいい」と思いがちですが、ALDは膜が厚くなるほど時間がかかりすぎて非効率です。厚い膜はCVDで一気に作り、極薄の重要な層だけALDで仕上げる──というように、適材適所で使い分けるのが半導体製造の鉄則です。

成膜装置の関連企業マップ──「世界4社の寡占構造」

🏭 装置・材料・ユーザーの3面で整理する

成膜装置の世界市場は、米国2社・日本2社の合計4社でほぼ独占されている寡占構造です。投資家視点で関連企業を3つの層に分けて整理しましょう。

装置メーカー(4強)

- Applied Materials(AMAT)

米・成膜装置の総合首位 - Lam Research(LRCX)

米・CVD/ALDで強い - 東京エレクトロン(8035)

日・成膜世界シェア約39% - KOKUSAI ELECTRIC(6525)

日・バッチ成膜で高シェア

材料メーカー

- 三菱ガス化学(4182)

HCD等の前駆体 - レゾナック(4004)

高純度ガス・材料 - ADEKA(4401)

High-k向け前駆体 - 大陽日酸(日本酸素HD)(4091)

特殊ガス供給

使う側(ユーザー)

- TSMC(2330.TW)

世界最大ファウンドリ - Samsung(005930.KS)

メモリ・ロジック両方 - Intel(INTC)

自社ファブ - SK Hynix(000660.KS)

HBM最大手 - Micron(MU)

米メモリ大手

📊 数字で見る寡占構造

成膜装置 世界シェア

装置 世界市場

市場規模(CAGR15%)

出典:装置市場はSEMI、東京エレクトロンのシェアは同社有報、薄膜成膜市場はMarket Researchを参照

成膜装置は1台数億〜数十億円する超高額品。しかもガス・温度・圧力・時間を精密に制御する技術ノウハウが膨大で、新規参入には数十年単位の経験が必要です。さらに半導体メーカーは「歩留まりが落ちると数百億円の損失」になるため、実績のあるメーカーから乗り換えるリスクを取りません。これが4社寡占を生む構造です。

あなたにとっての意味──投資家・学生・技術者の視点

成膜装置は、AI半導体の進化と需要が直結する領域です。GAAトランジスタ・3D NAND・HBMといった先端プロセスは、ALDやCVDの工程数が世代ごとに増えていきます。NVIDIAやTSMCの好調は、その裏で装置メーカー(AMAT、LRCX、東京エレクトロン、KOKUSAI ELECTRIC)と材料メーカーに構造的需要を生みます。「GPU銘柄」だけでなく、その上流の成膜装置・材料メーカーまで視野を広げると、AI投資の全体像が見えてきます。

成膜は「化学」「物理」「機械」「電気」が交差する分野です。化学系なら材料・前駆体の開発、物理系なら成膜メカニズムの解析、機械系なら装置設計、電気系なら制御──どの専攻でも参入余地があります。「半導体=情報系」というイメージを超えて、自分の専門が活きる場所を探してみてください。

成膜は前工程の中で露光・エッチングと並ぶ「3大重要工程」。歩留まりを左右する膜質ばらつき・パーティクル・前駆体管理といった現場ノウハウは、装置・材料・ファウンドリのどこで働いていても価値の高いスキルになります。担当外プロセスでも、シリーズ全体を読むことで前後工程との関係が見えるようになります。

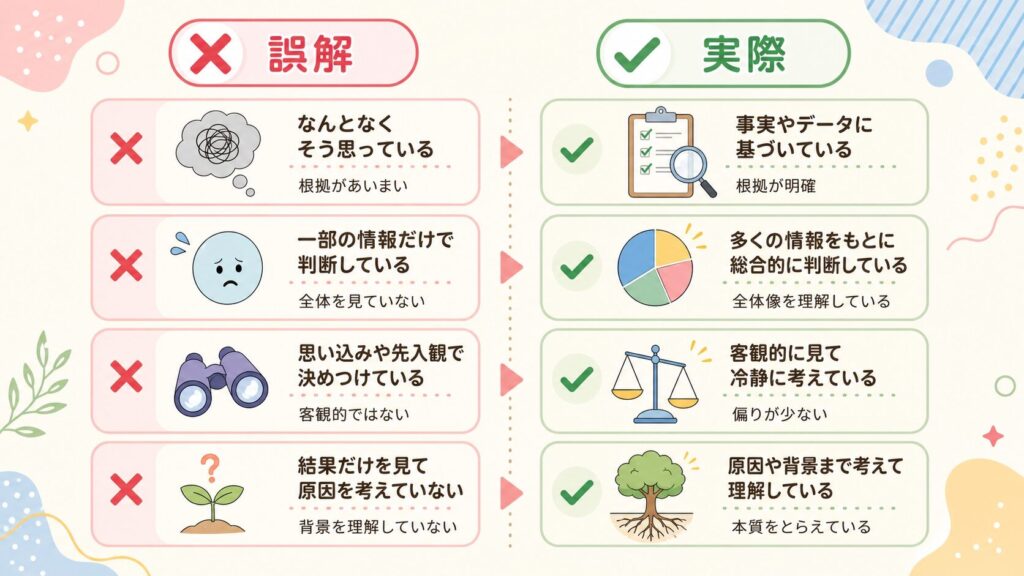

よくある誤解を整理する

| ❌ よくある誤解 | ✅ 実際はこう |

|---|---|

| 「成膜は1回やって終わり」 | 成膜→露光→エッチング→洗浄のサイクルを何十回も繰り返す。1枚のチップに数十〜100層以上の膜が積まれる。 |

| 「ALDが最強だから他は要らない」 | ALDは精度が究極だが速度が極端に遅い。厚い膜はCVD、金属はPVDで作るのが効率的。適材適所が鉄則。 |

| 「成膜と露光は同じようなもの」 | 成膜は「膜を作る」工程、露光は「膜にパターンを描く」工程。役割がまったく違う。両者がペアで働いて初めてチップができる。 |

| 「半導体装置と言えばASMLだけ」 | ASMLは露光装置の独占企業。成膜装置はAMAT・Lam・東京エレクトロン・KOKUSAI ELECTRICの4社が中心。工程ごとに支配企業が違う。 |

| 「日本企業はもう半導体で勝てない」 | 成膜装置では東京エレクトロンが世界シェア約39%、KOKUSAI ELECTRICもバッチ成膜で高シェア。装置・材料分野では日本が世界トップクラス。 |

まとめ:成膜の全体像

① 成膜とは:シリコンウェーハに数nm〜数百nmの極薄い膜を作る工程。前工程の中核。

② 役割:膜は「電気を通す」「電気を遮る」「特殊な機能を持つ」の3種類。1枚のチップに数十〜100層以上が積まれる。

③ 4つの方法:熱酸化(焼く)、CVD(蒸す)、PVD(貼り付ける)、ALD(1層ずつ塗る)。目的により使い分け。

④ 装置メーカー:AMAT・Lam Research・東京エレクトロン・KOKUSAI ELECTRICの4社が世界市場をほぼ独占する寡占構造。

⑤ 日本の強み:東京エレクトロンは成膜装置で世界シェア約39%。装置・材料分野で日本企業がトップクラス。

⑥ AI時代との接続:GAA・3D NAND・HBMで成膜工程数が増え続け、装置・材料の需要が構造的に拡大。

成膜は「膜を1層ずつ積み重ねる」というシンプルな発想に見えて、その精度は原子レベル。半導体の性能を根底で支える工程です。次の記事から、4つの成膜方法(熱酸化・CVD・PVD・ALD)を1つずつ深掘りしていきます。

❓ よくある質問(FAQ)

📚 次に読むべき記事

この記事は「成膜シリーズ」の入口(ピラー記事)です。次は4つの成膜方法を1つずつ深掘りしていきます。気になるものから読み進めてください。

🎓 成膜シリーズ全6記事

成膜の全体像と4つの方法を整理する入口記事

最も古典的な成膜法。SiO₂ゲート酸化膜を作る基本中の基本。

成膜の主力。LPCVDとPECVDの違いと使い分けを図解。

金属を物理的に弾き飛ばして膜にする方法。配線層の主役。

究極の精密成膜。AI半導体時代の成長領域。

業界構造の総括。投資家視点で4社寡占を解剖する。

📖 【完全図解】先端パッケージとは?AIチップの「組み立て方」が変わった理由 →

前工程(成膜含む)で作られたウェーハが、後工程でどう「組み立てられる」のか。先端パッケージの全体地図と接続できます。

📩 記事の更新情報を受け取りたい方へ

新しい記事が公開されたら、Xアカウント @shirasusolo でお知らせします。半導体プロセスの構造を一緒に学んでいきましょう。

コメント